Datasheet 搜索 > 放大器、缓冲器 > ADI(亚德诺) > ADA4505-2ACBZ-RL 数据手册 > ADA4505-2ACBZ-RL 其他数据使用手册 4/21 页

¥ 3.761

ADA4505-2ACBZ-RL 其他数据使用手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

放大器、缓冲器

封装:

WLCSP-8

描述:

10 μA ,轨至轨I / O,零输入交越失真放大器 10 μA, Rail-to-Rail I/O, Zero Input Crossover Distortion Amplifiers

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ADA4505-2ACBZ-RL数据手册

Page:

of 21 Go

若手册格式错乱,请下载阅览PDF原文件

ADA4857-1/ADA4857-2 Data Sheet

Rev. C | Page 4 of 20

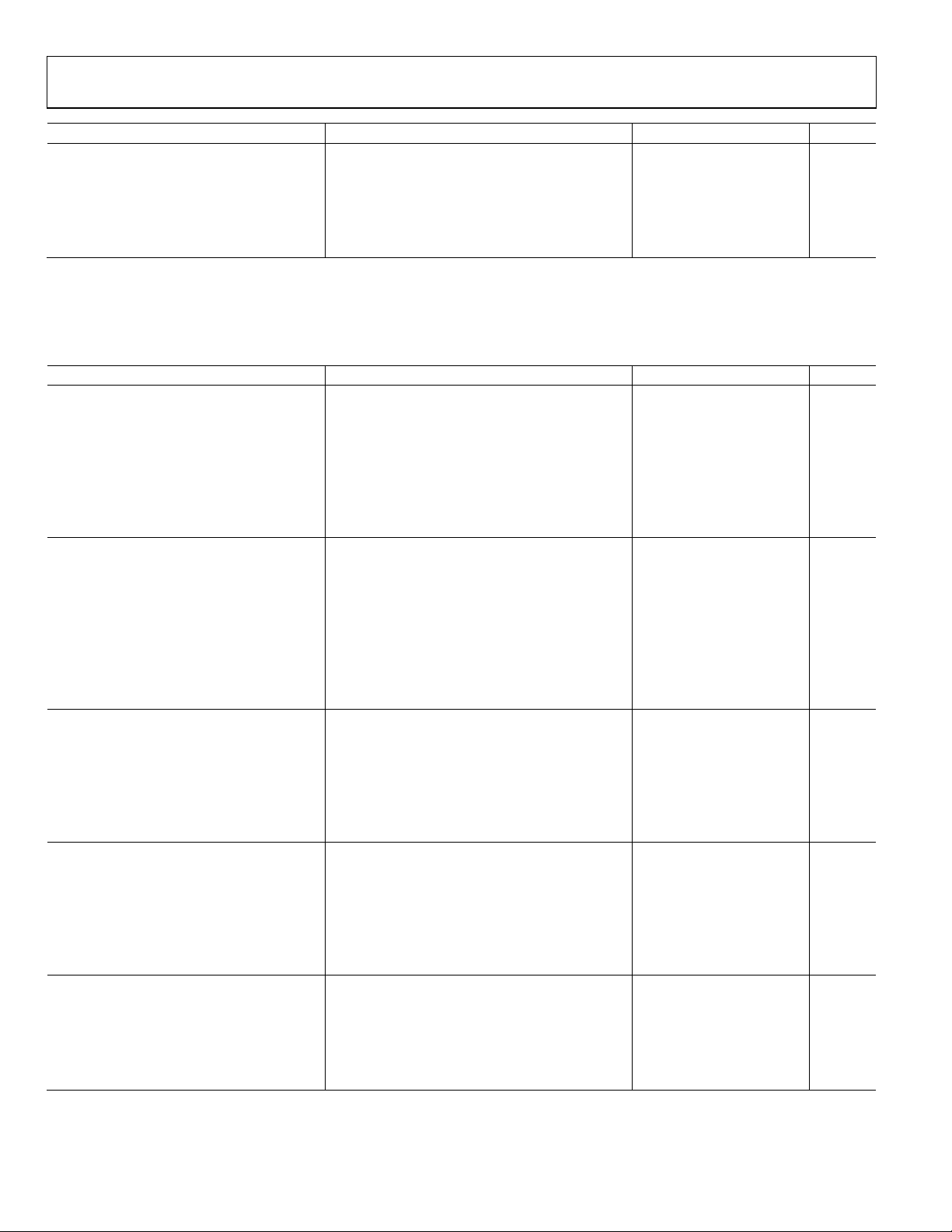

Parameter Conditions Min Typ Max Unit

POWER SUPPLY

Operating Range 4.5 10.5 V

Quiescent Current 5 5.5 mA

Quiescent Current (Power Down) PD ≥ V

CC

− 2 V 350 450 µA

Positive Power Supply Rejection

+V

S

= 4.5 V to 5.5 V, −V

S

= −5 V

−59

−62

dB

Negative Power Supply Rejection +V

S

= 5 V, −V

S

= −4.5 V to −5.5 V −65 −68 dB

+5 V SUPPLY

T

A

= 25°C, G = +2, R

F

= R

G

= 499 Ω, R

S

= 100 Ω for G = +1 (SOIC), R

L

= 1 kΩ to midsupply, PD = no connect, unless otherwise noted.

Table 2.

Parameter Conditions Min Typ Max Unit

DYNAMIC PERFORMANCE

–3 dB Bandwidth (LFCSP/SOIC) G = +1, V

OUT

= 0.2 V p-p 595 800/750 MHz

G = +1, V

OUT

= 2 V p-p 500/400 MHz

G = +2, V

OUT

= 0.2 V p-p 360/300 MHz

Full Power Bandwidth G = +1, V

OUT

= 2 V p-p, THD < −40 dBc 95 MHz

Bandwidth for 0.1 dB Flatness (LFCSP/SOIC)

G = +2, V

OUT

= 2 V p-p, R

L

= 150 Ω 50/40 MHz

Slew Rate (10% to 90%) G = +1, V

OUT

= 2 V step 1500 V/µs

Settling Time to 0.1% G = +2, V

OUT

= 2 V step 15 ns

NOISE/HARMONIC PERFORMANCE

Harmonic Distortion f = 1 MHz, G = +1, V

OUT

= 2 V p-p (HD2) −92 dBc

f = 1 MHz, G = +1, V

OUT

= 2 V p-p (HD3) −90 dBc

f = 10 MHz, G = +1, V

OUT

= 2 V p-p (HD2) −81 dBc

f = 10 MHz, G = +1, V

OUT

= 2 V p-p (HD3) −71 dBc

f = 50 MHz, G = +1, V

OUT

= 2 V p-p (HD2)

−69

dBc

f = 50 MHz, G = +1, V

OUT

= 2 V p-p (HD3) −55 dBc

Input Voltage Noise f = 100 kHz 4.4 nV/√Hz

Input Current Noise f = 100 kHz 1.5 pA/√Hz

DC PERFORMANCE

Input Offset Voltage ±1 ±4.2 mV

Input Offset Voltage Drift 4.6 µV/°C

Input Bias Current −1.7 −3.3 µA

Input Bias Current Drift 24.5 nA/°C

Input Bias Offset Current 50 nA

Open-Loop Gain V

OUT

= 1.25 V to 3.75 V 57 dB

PD (POWER-DOWN) PIN

PD Input Voltage Chip powered down ≥(V

CC

− 2) V

Chip enabled ≤(V

CC

− 4.2) V

Turn-Off Time 50% off PD to <10% of final V

OUT

, V

IN

= 1 V, G = +2 38 µs

Turn-On Time 50% off PD to <10% of final V

OUT

, V

IN

= 1 V, G = +2 30 ns

PD Pin Leakage Current

Chip enable

8

µA

Chip powered down 30 µA

INPUT CHARACTERISTICS

Input Resistance Common mode 8 MΩ

Differential mode 4 MΩ

Input Capacitance Common mode 2 pF

Input Common-Mode Voltage Range 1 to 4 V

Common-Mode Rejection Ratio V

CM

= 2 V to 3 V −76 −84 dB

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件