Datasheet 搜索 > EEPROM芯片 > ATMEL(爱特美尔) > AT24C02C-SSHM-T 数据手册 > AT24C02C-SSHM-T 产品手册 6/23 页

器件3D模型

器件3D模型¥ 0.834

AT24C02C-SSHM-T 产品手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

EEPROM芯片

封装:

SOIC-8

描述:

ATMEL AT24C02C-SSHM-T EEPROM, 2 Kbit, 256K x 8位, 1 MHz, I2C, SOIC, 8 引脚

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

AT24C02C-SSHM-T数据手册

Page:

of 23 Go

若手册格式错乱,请下载阅览PDF原文件

6

8700D–SEEPR–8/10

Atmel AT24C02C

3. Device Operation

CLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external device. Data on the SDA

pin may change only during SCL low time periods (see Figure 5-2 on page 8). Data changes during SCL high

periods will indicate a start or stop condition as defined below.

START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any

other command (see Figure 5-3 on page 8).

STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the

stop command will place the EEPROM in a standby power mode (see Figure 5-3 on page 8).

ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words.

The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock

cycle.

STANDBY MODE: The Atmel

®

AT24C02C features a low-power standby mode which is enabled: (a) upon power-

up and (b) after the receipt of the STOP bit and the completion of any internal operations.

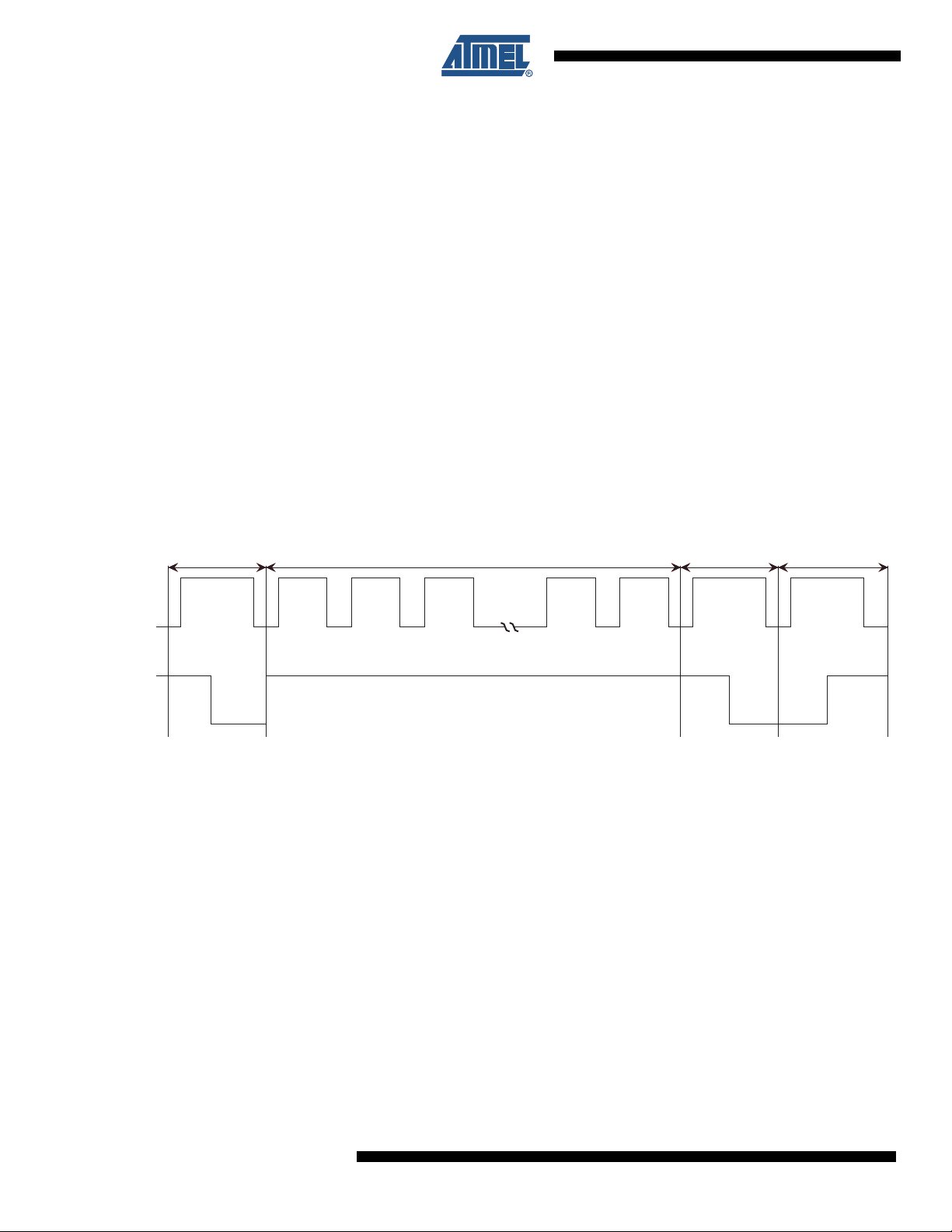

2-Wire Software Reset: After an interruption in protocol, power loss or system reset, any 2-wire part can be reset

by following these steps: (a) Create a start bit condition, (b) clock 9 cycles, (c) create another start bit followed by

stop bit condition as shown below. The device is ready for next communication after above steps have been

completed.

Figure 3-1. Software reset

Start bit

Stop bitStart bitDummy Clock Cycles

SCL

SDA

123 89

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件