Datasheet 搜索 > 数模转换器 > Cirrus Logic(思睿逻辑) > CS5343-DZZR 数据手册 > CS5343-DZZR 其他数据使用手册 6/24 页

器件3D模型

器件3D模型¥ 13.86

CS5343-DZZR 其他数据使用手册 - Cirrus Logic(思睿逻辑)

制造商:

Cirrus Logic(思睿逻辑)

分类:

数模转换器

封装:

TSSOP-10

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

典型应用电路图在P7

原理图在P14

导航目录

CS5343-DZZR数据手册

Page:

of 24 Go

若手册格式错乱,请下载阅览PDF原文件

6 DS687DB2

CDB5343

8. CONNECTORS

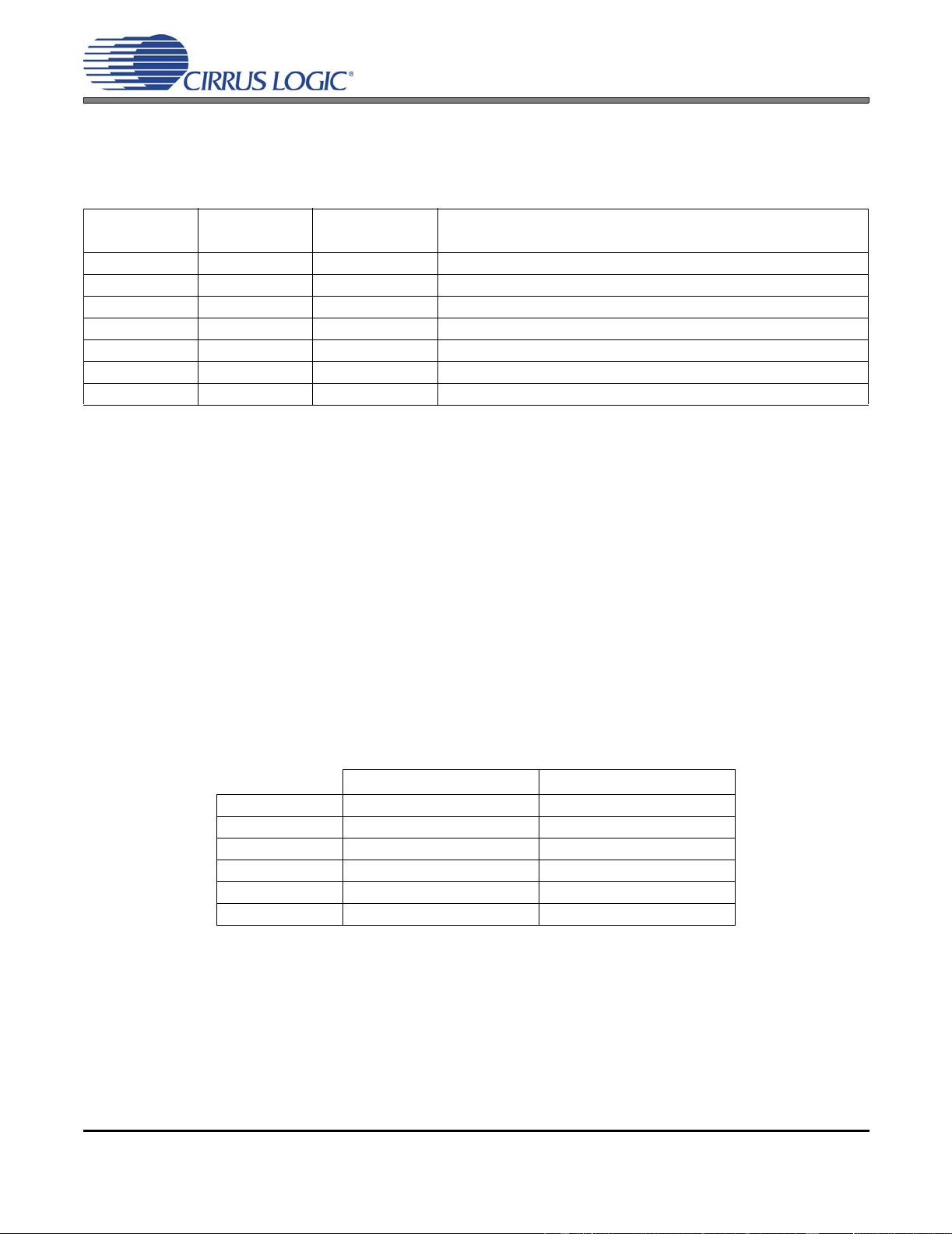

Table 1 lists the connectors on the CDB5343, the reference designator of each connector, the directionality, and

the associated signal.

9. JUMPER AND SWITCH SETTINGS

The user can fully configure the CDB5343 with a bank of six DIP switches (S1) and a single jumper setting on header

J4.

9.1 Jumper J4

This jumper selects the magnitude of VA, either 3.3 V or 5 V. The CS5343 is a single-supply device; there-

fore the magnitude of VA affects the full-scale analog input voltage as well as the digital I/O voltage. Digital

I/O is always fixed at VA, and the full-scale input is nominally 0.56xVA Vpp, as specified in the CS5343 data

sheet. If the user selects 5 V, the CS5343 full-scale analog input voltage is 2.82 Vpp (1 Vrms) and the digital

I/O is set to 5 V. If 3.3 V is selected, the full-scale analog input voltage is 1.86 Vpp (660 mVrms) and digital

I/O is 3.3 V.

9.2 Switch S1

Table 2 shows the available settings for S1 with the default settings.

9.2.1 CS5343

This switch configures the CS5343 for either Master Mode or Slave Mode operation. When set as clock

Master, the CS8406 must be set to “Slave” and “SCLK, LRCK” must be set to “TO HDR.” When CS5343

is configured for Slave Mode, the CS8406 must be set for Master Mode, or “SCLK, LRCK” must be set to

“FROM HDR.”

CONNECTOR

REFERENCE

DESIGNATOR INPUT/OUTPUT SIGNAL

+5V J2 INPUT +5 V power to crystal oscillator and DC voltage regulator

GND J1 INPUT Ground connection from the power supply

AINR J7 INPUT Analog input right channel

AINL J5 INPUT Analog input left channel

Co-axial J6 OUTPUT Digital audio (S/PDIF) output

Optical J9 OUTPUT Digital audio (S/PDIF) output

I/O HDR J3 INPUT/OUTPUT Master Clock, Serial Clock, Left/Right Clock, SDOUT

Table 1. System Connections

OPEN CLOSED

CS5343 MASTER (default) SLAVE

CS8406 MASTER SLAVE (default)

MCLK FROM HDR TO HDR (default)

SCLK, LRCK FROM HDR TO HDR (default)

SPEED DSM SSM (default)

MCLK/LRCK 256x (default) 384x

Table 2. CDB5343 S1 Settings

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件