Datasheet 搜索 > Cirrus Logic(思睿逻辑) > CS5460A-BS 数据手册 > CS5460A-BS 其他数据使用手册 6/54 页

¥ 5.257

CS5460A-BS 其他数据使用手册 - Cirrus Logic(思睿逻辑)

制造商:

Cirrus Logic(思睿逻辑)

封装:

SOIC-8

描述:

电流和电力监控器、调节器 Single-Phase Bi-Dir Power/Energy IC

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

CS5460A-BS数据手册

Page:

of 54 Go

若手册格式错乱,请下载阅览PDF原文件

CS5460A

6 DS487F4

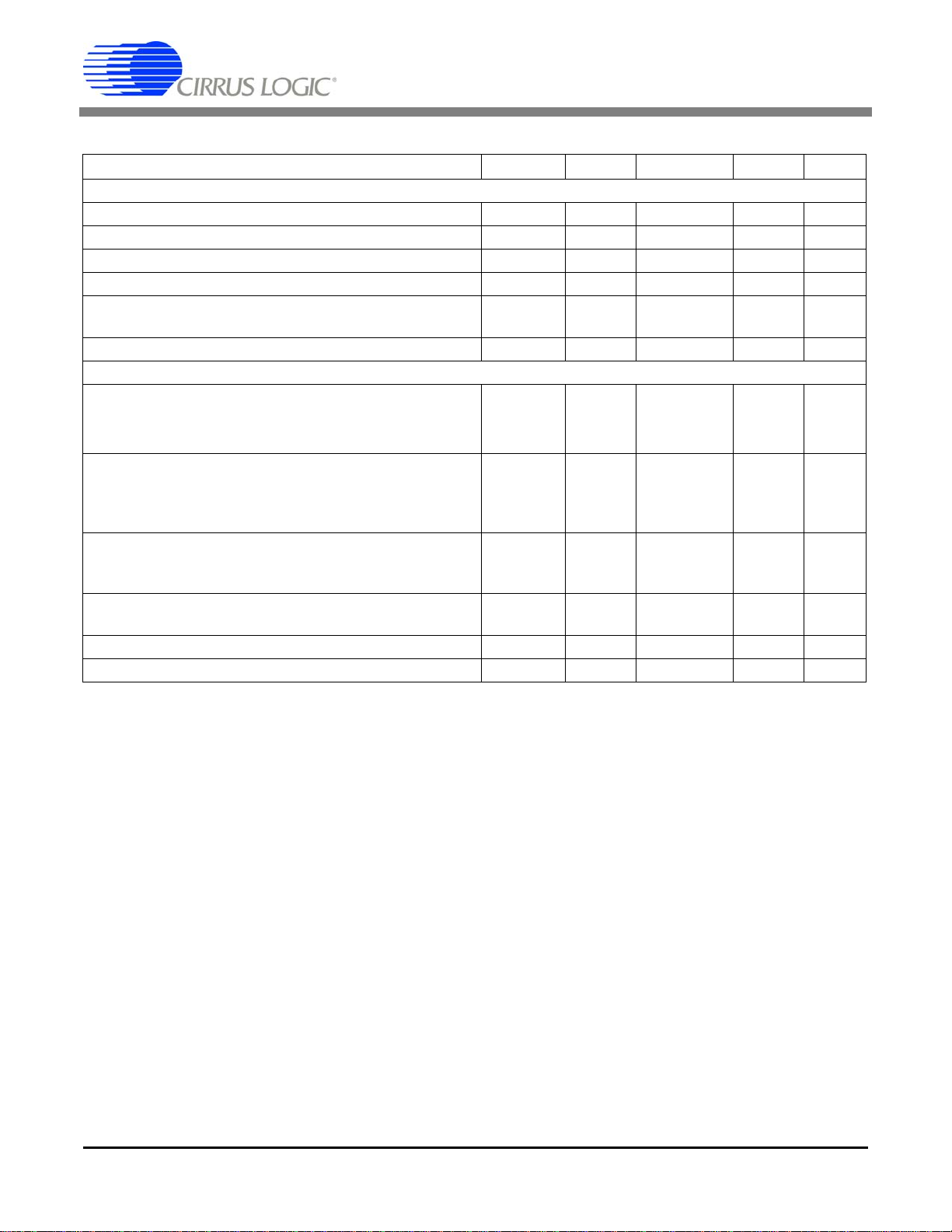

ANALOG CHARACTERISTICS (Continued)

Notes: 7. The minimum FSCR is limited by the maximum allowed gain register value.

8. All outputs unloaded. All inputs CMOS level.

9. Definition for PSRR: VREFIN tied to VREFOUT, VA+ = VD+ = 5 V, a 150 mV zero-to-peak sinewave

(frequency = 60 Hz) is imposed onto the +5 V supply voltage at VA+ and VD+ pins. The “+” and “-” input

pins of both input channels are shorted to VA-. Then the CS5460A is commanded to ’continuous

computation cycles’ data acquisition mode, and digital output data is collected for the channel under

test. The zero-peak value of the digital sinusoidal output signal is determined, and this value is

converted into the zero-peak value of the sinusoidal voltage that would need to be applied at the

channel’s inputs, in order to cause the same digital sinusoidal output. This voltage is then defined as

Veq. PSRR is then (in dB):

10. When voltage level on PFMON is sagging, and LSD bit is 0, the voltage at which LSD bit is set to 1.

11. Assuming that the LSD bit has been set to 1 (because PFMON voltage fell below PMLO), then if/when

the PFMON voltage starts to rise again, PMHI is the voltage level (on PFMON pin) at which the LSD bit

can be permanently reset back to 0 (without instantaneously changing back to 1). Attempts to reset the

LSD bit before this condition is true will not be successful. This condition indicates that power has been

restored. Typically, for a given sample, the PMHI voltage will be ~100 mV above the PMLO voltage.

Parameter Symbol Min Typ Max Unit

Dynamic Characteristics

Phase Compensation Range (Voltage Channel, 60 Hz) -2.4 - +2.5 °

High Rate Filter Output Word Rate (Both Channels) OWR - DCLK/1024 - Sps

Input Sample Rate DCLK = MCLK/K - DCLK/8 - Sps

Full Scale DC Calibration Range (Note 7) FSCR 25 - 100 %F.S.

Channel-to-Channel Time-Shift Error

(when PC[6:0] bits are set to “0000000”)

1.0 µs

High Pass Filter Pole Frequency -3 dB - 0.5 - Hz

Power Supplies

Power Supply Currents (Active State) I

A+

I

D+

(VD+ = 5 V)

I

D+

(VD+ = 3.3 V)

PSCA

PSCD

PSCD

-

-

-

1.3

2.9

1.7

-

-

-

mA

mA

mA

Power Consumption Active State (VD+ = 5 V)

(Note 8) Active State (VD+ = 3.3 V)

Stand-By State

Sleep State

PC -

-

-

-

21

11.6

6.75

10

25

-

-

-

mW

mW

mW

µW

Power Supply Rejection Ratio (50, 60 Hz)

for Current Channel (Gain = 10)

(Note 9) (Gain = 50)

PSRR

PSRR

56

75

-

-

-

-

dB

dB

Power Supply Rejection Ratio (50, 60 Hz)

for Voltage Channel (Note 9) PSRR - 65 - dB

PFMON Power-Fail Detect Threshold (Note 10) PMLO 2.3 2.45 - V

PFMON “Power-Restored” Detect Threshold (Note 11) PMHI - 2.55 2.7 V

PSRR 20

0.150V

V

eq

-------------------

⎩⎭

⎨⎬

⎧⎫

log⋅=

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件