Datasheet 搜索 > DA转换器 > TI(德州仪器) > DAC7512E/2K5 数据手册 > DAC7512E/2K5 其他数据使用手册 5/24 页

器件3D模型

器件3D模型¥ 7.371

DAC7512E/2K5 其他数据使用手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

DA转换器

封装:

VSSOP-8

描述:

低功耗,轨到轨输出, 12位串行输入数位类比转换器 Low-Power, Rail-to-Rail Output, 12-Bit Serial Input DIGITAL-TO-ANALOG CONVERTER

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

封装尺寸在P24

功能描述在P7

导航目录

DAC7512E/2K5数据手册

Page:

of 24 Go

若手册格式错乱,请下载阅览PDF原文件

Rev. F | Page 5 of 24

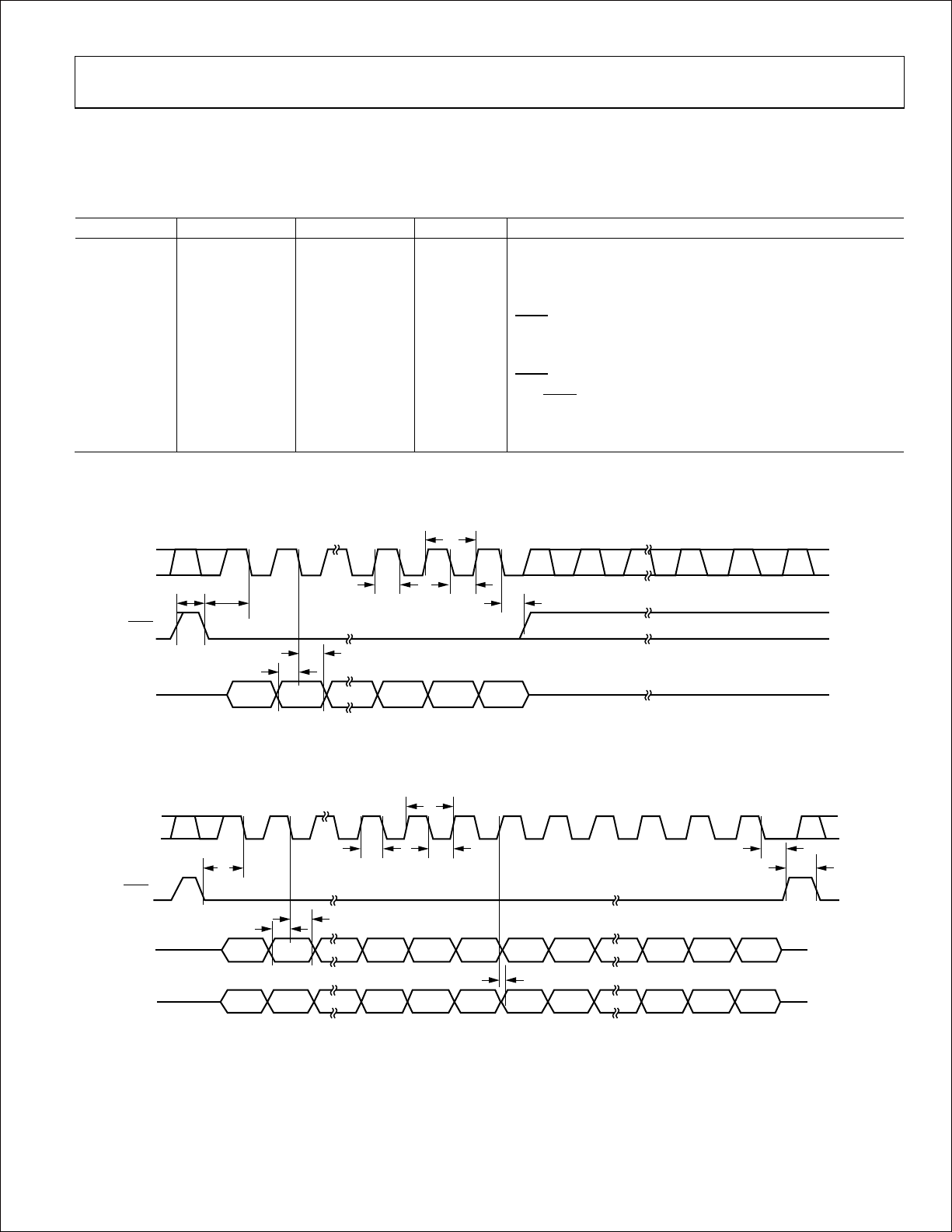

表2.

参数 2.5 V至5.5 V 4.5 V至5.5 V 单位 测试条件/注释

f

SCLK

50 50 MHz(最大值) 最大时钟频率

t

1

20 20 ns(最小值) SCLK周期时间

t

2

8 8 ns(最小值) SCLK高电平时间

t

3

8 8 ns(最小值) SCLK低电平时间

t

4

1

13 13 ns(最小值)

SYNC 下降沿到SCLK有效沿建立时间

t

5

5 5 ns(最小值) 数据建立时间

t

6

3 3 ns(最小值) 数据保持时间

t

7

5 5 ns(最小值)

SYNC 上升沿到SCL有效沿

t

8

30 30 ns(最小值)

最小SYNC高电平时间

t

9

2, 3

80 45 ns(典型值) SCLK有效沿到SDO有效

120 65 ns(最大值)

DB15 DB0

SCLK

SYNC

DIN

ALTERNATIVELY, DATA MAY BE CLOCKED INTO INPUT SHIFT REGISTER ON RISING EDGE OF

SCLK AS DETERMINED BY CONTROL BITS. TIMING AS PER ABOVE, WITH SCLK INVERTED.

t

1

t

8

t

4

t

3

t

2

t

5

t

6

t

7

03162-002

图2. 独立模式时序图

DB15 (N) DB0 (N)

DB15

(N + 1)

DB0

(N + 1)

SCLK

SDIN

SDO

ALTERNATIVELY, DATA MAY BE CLOCKED INTO INPUT SHIFT REGISTER ON RISING EDGE OF SCLK AS

DETERMINED BY CONTROL BITS. IN THIS CASE, DATA WOULD BE CLOCKED OUT OF SDO ON FALLING

EDGE OF SCLK. TIMING AS PER ABOVE, WITH SCLK INVERTED.

t6

DB15(N)

DB0(N)

t

1

t

2

t

5

t

9

t

6

t

4

t

3

t

7

t

8

SYNC

03162-003

图3. 菊花链和回读模式时序图

AD5426/AD5432/AD5443

时序特性

所有输入信号均指定t

r

= t

f

= 1 ns(10%至90%的V

DD

),并从(V

IL

+ V

IH

)/2电平开始。V

DD

= 2.5 V至5.5 V,V

REF

= 10 V,I

OUT

2 = 0 V;

Y级温度范围:−40°C至+125°C;所有规格均相对于T

MIN

至T

MAX

而言,除非另有说明。

1

下降或上升沿由串行字的控制位决定。

2

菊花链和回读模式无法在最大时钟频率下工作。SDO时序规格采用负载电路测量,如图4所示。

3

SDO工作电压为VDD = 3.0 V至5.5 V。

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件