Datasheet 搜索 > EEPROM芯片 > ST Microelectronics(意法半导体) > M24C04-DRDW3TP/K 数据手册 > M24C04-DRDW3TP/K 其他数据使用手册 6/43 页

器件3D模型

器件3D模型¥ 2.603

M24C04-DRDW3TP/K 其他数据使用手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

分类:

EEPROM芯片

封装:

TSSOP-8

描述:

EEPROM, 4 Kbit, 512 x 8位, 串行I2C (2-线), 1 MHz, TSSOP, 8 引脚

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

M24C04-DRDW3TP/K数据手册

Page:

of 43 Go

若手册格式错乱,请下载阅览PDF原文件

Description M24C04-DRE

6/42 DocID027421 Rev 2

1 Description

The M24C04-DRE is a 4-Kbit serial EEPROM device operating up to 105 °C. The M24C04-

DRE is compliant with the level of reliability defined by the AEC-Q100 grade 2.

The device is accessed by a simple serial I

2

C compatible interface running up to 1 MHz.

The memory array is based on advanced true EEPROM technology (electrically erasable

programmable memory). The M24C04-DRE is a byte-alterable memory (512 × 8

bits)

organized as 32

pages of 16 bytes in which the data integrity is significantly improved with

an embedded Error Correction Code logic.

The M24C04-DRE offers an additional Identification Page (16 bytes) in which the ST device

identification can be read. This page can also be used to store sensitive application

parameters which can be later permanently locked in read-only mode.

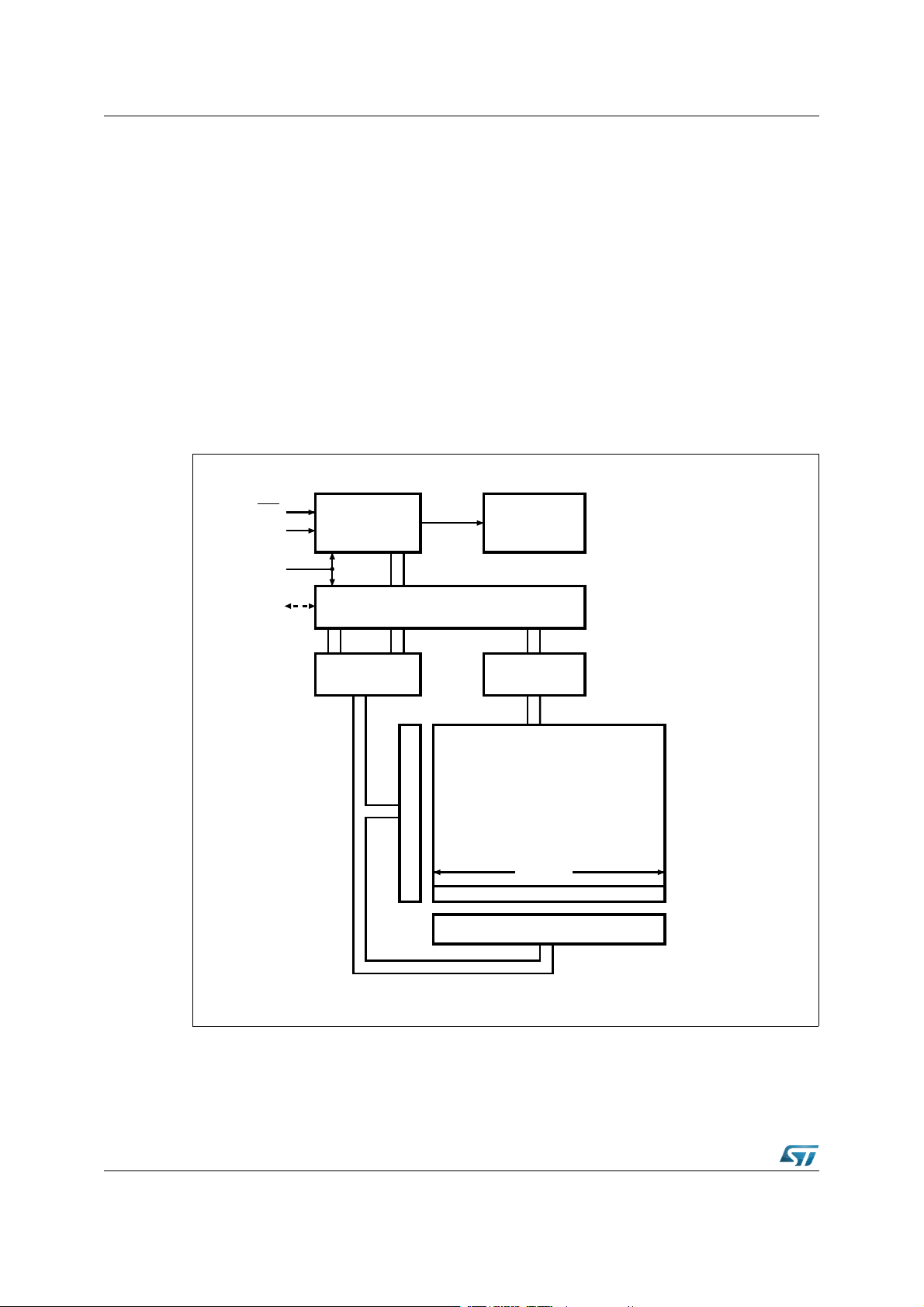

Figure 1. Logic diagram

-36

7#

#ONTROLLOGIC

(IGHVOLTAGE

GENERATOR

)/SHIFTREGISTER

!DDRESSREGISTER

ANDCOUNTER

$ATA

REGISTER

PAGE

8DECODER

9DECODER

)DENTIFICATIONPAGE

%I

3#,

3$!

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件