Datasheet 搜索 > 接口芯片 > Maxim Integrated(美信) > MAX3421EETJ+ 数据手册 > MAX3421EETJ+ 其他数据使用手册 3/63 页

器件3D模型

器件3D模型¥ 110.81

MAX3421EETJ+ 其他数据使用手册 - Maxim Integrated(美信)

制造商:

Maxim Integrated(美信)

分类:

接口芯片

封装:

TQFN-32

描述:

MAXIM INTEGRATED PRODUCTS MAX3421EETJ+ 接口, USB, USB主机/外设控制器, USB 2.0, 3 V, 3.6 V, TQFN, 32 引脚

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P18Hot

导航目录

MAX3421EETJ+数据手册

Page:

of 63 Go

若手册格式错乱,请下载阅览PDF原文件

3

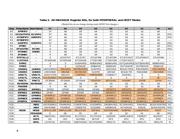

Table 1. MAX3421E HOST Registers (Host Bit = 1)

Reg Name b7 b6 b5 b4 b3 b2 b1 b0 acc

R0 — 0 0 0 0 0 0 0 0 —

R1

RCVFIFO

b7 b6 b5 b4 b3 b2 b1 b0 RSC

R2

SNDFIFO

b7 b6 b5 b4 b3 b2 b1 b0 RSC

R3 — 0 0 0 0 0 0 0 0 —

R4

SUDFIFO

b7 b6 b5 b4 b3 b2 b1 b0 RSC

R5 — 0 0 0 0 0 0 0 0 RSC

R6

RCVBC

0 b6 b5 b4 b3 b2 b1 b0 RSC

R7

SNDBC

0 b6 b5 b4 b3 b2 b1 b0 —

R8 — 0 0 0 0 0 0 0 0 —

R9 — 0 0 0 0 0 0 0 0 —

R10 — 0 0 0 0 0 0 0 0 —

R11 — 0 0 0 0 0 0 0 0 —

R12 — 0 0 0 0 0 0 0 0 RSC

R13

USBIRQ

0 VBUSIRQ NOVBUSIRQ 0 0 0 0 OSCOKIRQ RC

R14

USBIEN

0 VBUSIE NOVBUSIE 0 0 0 0 OSCOKIE RSC

R15

USBCTL

0 0 CHIPRES PWRDOWN 0 0 0 0 RSC

R16

CPUCTL

PULSEWID1 PULSEWID0 0 0 0 0 0 IE RSC

R17

PINCTL

0 0 0 FDUPSPI INTLEVEL POSINT GPXB GPXA RSC

R18

REVISION

b7 b6 b5 b4 b3 b2 b1 b0 R

R19 — 0 0 0 0 0 0 0 0 —

R20

IOPINS1

GPIN3 GPIN2 GPIN1 GPIN0 GPOUT3 GPOUT2 GPOUT1 GPOUT0 RSC

R21

IOPINS2

GPIN7 GPIN6 GPIN5 GPIN4 GPOUT7 GPOUT6 GPOUT5 GPOUT4 RSC

R22

GPINIRQ

GPINIRQ7 GPINIRQ6 GPINIRQ5 GPINIRQ4 GPINIRQ3 GPINIRQ2 GPINIRQ1 GPINIRQ0 RC

R23

GPINIEN

GPINIEN7 GPINIEN6 GPINIEN5 GPINIEN4 GPINIEN3 GPINIEN2 GPINIEN1 GPINIEN0 RSC

R24

GPINPOL

GPINPOL7 GPINPOL6 GPINPOL5 GPINPOL4 GPINPOL3 GPINPOL2 GPINPOL1 GPINPOL0 RSC

R25

HIRQ

HXFRDNIRQ FRAMEIRQ CONDETIRQ SUSDNIRQ SNDBAVIRQ RCVDAVIRQ RWUIRQ BUSEVENTIRQ RC

R26

HIEN

HXFRDNIE FRAMEIE CONDETIE SUSDNIE SNDBAVIE RCVDAVIE RWUIE BUSEVENTIE RSC

R27

MODE

DPPULLDN DMPULLDN DELAYISO SEPIRQ SOFKAENAB HUBPRE LOWSPEED HOST RSC

R28

PERADDR

0 b6 b5 b4 b3 b2 b1 b0 RSC

R29

HCTL

SNDTOG1 SNDTOG0 RCVTOG1 RCVTOG0 SIGRSM SAMPLEBUS FRMRST BUSRST LS

R30

HXFR

HS ISO OUTNIN SETUP EP3 EP2 EP1 EP0 LS

R31

HRSL

JSTATUS KSTATUS SNDTOGRD RCVTOGRD HRSLT3 HRSLT2 HRSLT1 HRSLT0 R

Setting the HOST bit (R27 bit 0) to 1 changes the MAX3420E register map in three ways. It redefines registers R0 through R7, clears

certain bits that do not apply to host operation, and adds registers 25, 26, and 28 through 31. Bits shown with 0 in Table 1 above

should be written with 0 in host mode. For clarity, the unused peripheral registers and bits are shown with zeros.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件