Datasheet 搜索 > 运算放大器 > Microchip(微芯) > MCP604T-I/ST 数据手册 > MCP604T-I/ST 其他数据使用手册 4/66 页

器件3D模型

器件3D模型¥ 7.874

MCP604T-I/ST 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

运算放大器

封装:

TSSOP-14

描述:

MCP604系列 6V 2.8MHz 单电源 CMOS 运算放大器-TSSOP-14

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P25Hot

典型应用电路图在P1P28

原理图在P34

标记信息在P57

封装信息在P57P63

功能描述在P31

技术参数、封装参数在P4P5P6P43

应用领域在P1P28P29

电气规格在P4P5P6P43

导航目录

MCP604T-I/ST数据手册

Page:

of 66 Go

若手册格式错乱,请下载阅览PDF原文件

MCP2030

DS21981A-page 4 © 2005 Microchip Technology Inc.

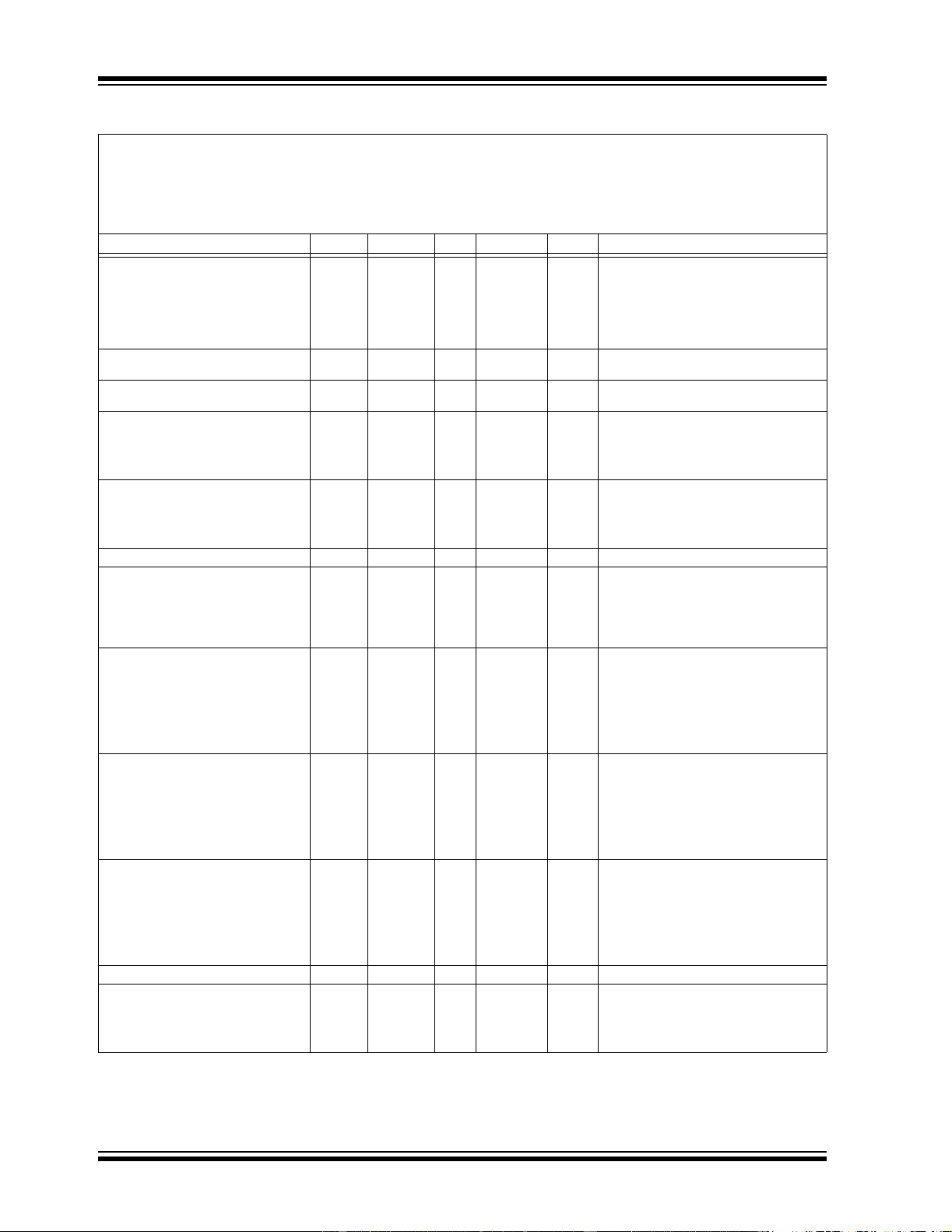

AC Characteristics

Electrical Specifications: Standard Operating Conditions (unless otherwise stated)

Supply Voltage 2.0V ≤ V

DD

≤ 3.6V

Operating temperature -40°C ≤ T

A

≤ +85°C

LCCOM connected to V

SS

LC Signal Input Sinusoidal 300 mV

PP

Carrier Frequency 125 kHz

LCCOM connected to V

SS

Parameters Sym. Min. Typ† Max. Units Conditions

Input Sensitivity V

SENSE

13.0 6mV

PP

V

DD

= 3.0V

Output enable filter disabled

AGCSIG = 0; MODMIN = 00

(33% modulation depth setting)

Input = Continuous Wave (CW)

Output = Logic level transition from

low-to-high at sensitivity level for CW input.

Coil de-Q’ing Voltage -

RF Limiter (R

FLM

) must be active

V

DE_Q

3— 5 VV

DD

= 3.0V, Force I

IN

= 5 μA (worst case)

RF Limiter Turn-on Resistance

(LCX, LCY, LCZ)

R

FLM

— 300 700 Ω V

DD

= 2.0V, V

IN

= 8 V

DC

Sensitivity Reduction S

ADJ

—

—

0

-30

—

—

dB

dB

V

DD

= 3.0V

No sensitivity reduction selected

Max. reduction selected

Monotonic increment in attenuation value

from setting = 0000 to 1111 by design

Minimum Modulation Depth

60% setting

33% setting

14% setting

8%

V

IN_MOD

—

—

—

60

33

14

8

84

49

26

%

%

%

%

V

DD

= 3.0V

See Section 5.21 “Minimum Modulation

Depth Requirement for Input Signal”.

See Modulation Depth Definition in

Figure 5-5.

Carrier frequency F

CARRIER

—125 — kHz

Input modulation frequency F

MOD

— — 10 kHz Input data rate with NRZ data format.

V

DD

= 3.0V

Minimum modulation depth setting = 33%

Input conditions:

Amplitude = 300 mV

PP

Modulation depth = 100%

LCX Tuning Capacitor C

TUNX

—

44

0

59

—

82

pF

pF

V

DD

= 3.0V,

Config. Reg. 1, bits <6:1> Setting = 000000

63 pF ±30%

Config. Reg. 1, bits <6:1> Setting = 111111

63 steps, approx. 1 pF/step

Monotonic increment in capacitor value from

setting = 000000 to 111111 by design

LCY Tuning Capacitor C

TUNY

—

44

0

59

—

82

pF

pF

V

DD

= 3.0V,

Config. Reg. 2, bits <6:1> Setting = 000000

63 pF ±30%

Config. Reg. 2, bits <6:1> Setting = 111111

63 steps, approx. 1 pF/step

Monotonic increment in capacitor value from

setting = 000000 to 111111 by design

LCZ Tuning Capacitor C

TUNZ

—

44

0

59

—

82

pF

pF

V

DD

= 3.0V,

Config. Reg. 3, bits<6:1> Setting = 000000

63 pF ±30%

Config. Reg. 3, bits<6:1> Setting = 111111

63 steps, approx. 1 pF/step

Monotonic increment in capacitor value from

setting = 000000 to 111111 by design

Q of Internal Tuning Capacitors Q_C 50 * — —

Demodulator Charge Time

(delay time of demodulated output to rise)

T

DR

—50 — μsV

DD

= 3.0V

Minimum modulation depth setting = 33%

Input conditions:

Amplitude = 300 mV

PP

Modulation depth = 100%

* Parameter is characterized but not tested.

† Data in “Typ” column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Required output enable filter high time must account for input path analog delays (= T

OEH

- T

DR

+ T

DF

).

2: Required output enable filter low time must account for input path analog delays (= T

OEL

+ T

DR

- T

DF

).

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件