Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC16C74A-20I/PQ 数据手册 > PIC16C74A-20I/PQ 其他数据使用手册 5/8 页

器件3D模型

器件3D模型¥ 114.123

PIC16C74A-20I/PQ 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

QFP-44

描述:

8位CMOS微控制器与A / D转换器 8-Bit CMOS Microcontrollers with A/D Converter

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

技术参数、封装参数在P5

导航目录

PIC16C74A-20I/PQ数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

2001 Microchip Technology Inc. DS80089A-page 5

PIC16C74A

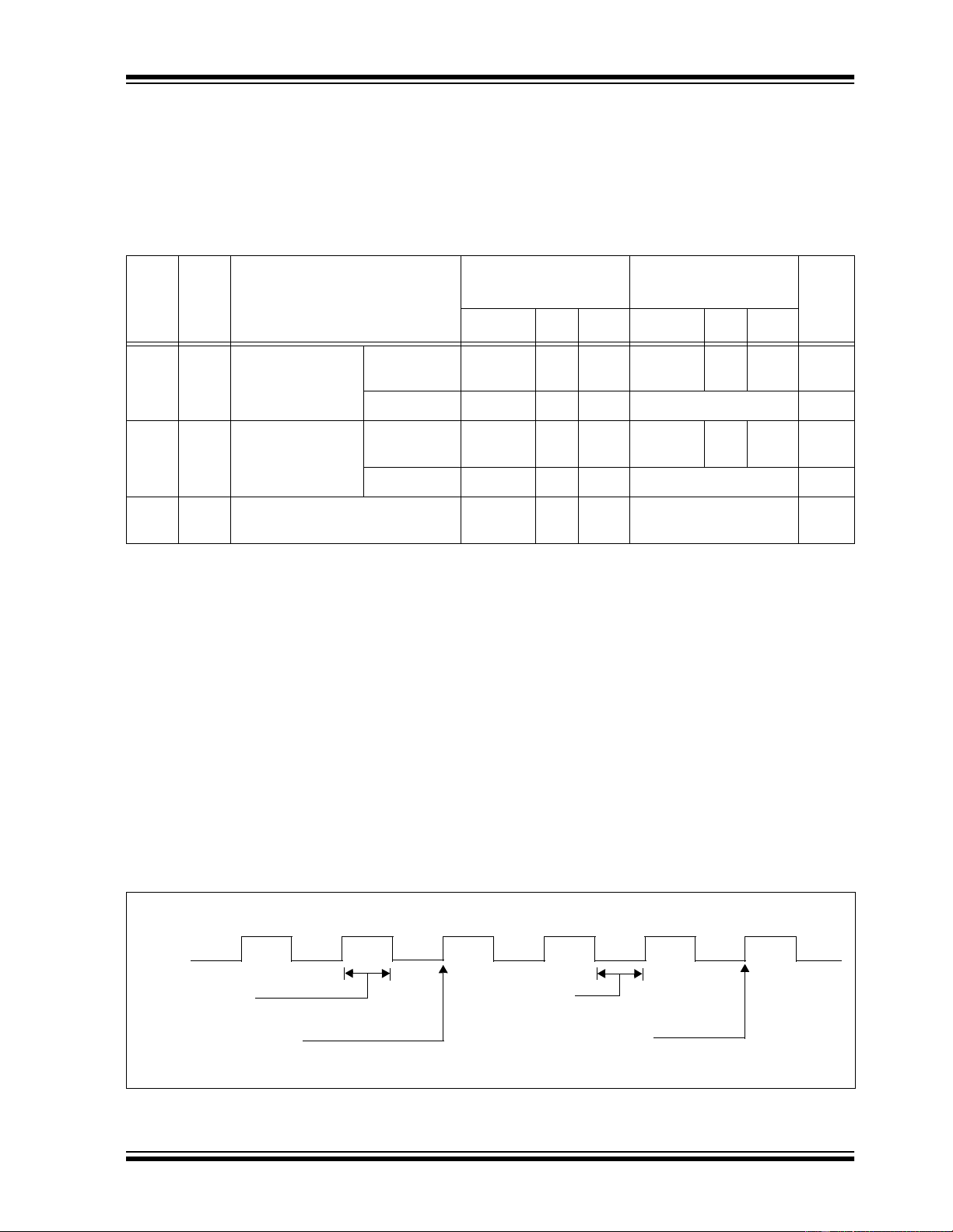

3. Module: SSP (SPI

TM

Mode Timing

Specifications)

The SPI interface timings (parameters 71, 71A, 72,

72A, 73, and 73A) have been modified. The new

values are shown in Table 3.

TABLE 3: DC SPECIFICATION CHANGES FROM DATA SHEET

4. Module: Timer1

The operation of Timer1 needs some clarification

when the timer registers are written when the

TMR1ON bit is set.

The internal clock signal that is the input to the

TMR1 prescaler affects the incrementing of Timer1

(TMR1H:TMR1L registers and the Timer1 pres-

caler). When the Timer1 registers are NOT written,

the Timer1 will increment on the rising edge of the

TMR1 increment clock.

When the TMR1H and/or TMR1L registers are

written while this clock is high, TMR1 will incre-

ment on the next rising edge of this clock.

When the TMR1H and/or TMR1L registers are

written while this clock is low, TMR1 will not incre-

ment on the next rising edge of this clock, but must

first have a falling clock and the rising clock, for

TMR1 to increment.

Figure 1 shows the two cases of writes to the

TMR1H and/or TMR1L registers. Due to the V

IH

and VIL thresholds on the oscillator/clock pins,

external Timer1 oscillator components, and exter-

nal clock frequency, the Timer1 increment clock

may not be of a 50% duty cycle.

The TMR1 increment clock is out of phase of the

T1OSO/T1CKI pin by a small propagation delay.

FIGURE 1: WRITES TO TIMER1 (EXTERNAL CLOCK/OSCILLATOR MODE)

Param

No.

Sym. Characteristic

New Specification

Data Sheet

Specification

Units

Min Typ Max Min Typ Max

71

T

SCH

SCK input high time

(slave mode)

Continuous

1.25 T

CY

+ 30 ns

——

T

CY

+ 20 ns

——

ns

71A Single Byte

(1)

40 —— N.A. ns

72

T

SCL

SCK input low time

(slave mode)

Continuous

1.25 T

CY

+ 30 ns

——

T

CY

+ 20 ns

——

ns

72A Single Byte

(1)

40 —— N.A. ns

73A T

B2B

Last clock edge of the Byte1 to 1st

clock edge of the Byte2

(1)

1.5 TCY

+ 40 ns

—— N.A.

ns

* This parameter is characterized but not tested.

Note 1: Specification 73A is only required if specifications 71A and 72A are used.

TMR1 Increment

Write to TMR1H

TMR1H:TMR1L Increments

Write to TMR1H

TMR1H:TMR1L Increments

Clock (Input to Prescaler)

and/or TMR1L Register(s)

and/or TMR1L Register(s)

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件