Datasheet 搜索 > 微控制器 > ST Microelectronics(意法半导体) > STM32F412RET6 数据手册 > STM32F412RET6 产品设计参考手册 5/159 页

器件3D模型

器件3D模型¥ 11.753

STM32F412RET6 产品设计参考手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

分类:

微控制器

封装:

LQFP-64

描述:

STM32F412RET6可运行于工作频率100 MHz、支持浮点运算单元的Cortex-M4内核,在运行和停机模式下实现出色的低功耗性能。

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P88

功能描述在P136

应用领域在P89

导航目录

STM32F412RET6数据手册

Page:

of 159 Go

若手册格式错乱,请下载阅览PDF原文件

5

32002F–03/2010

AVR32

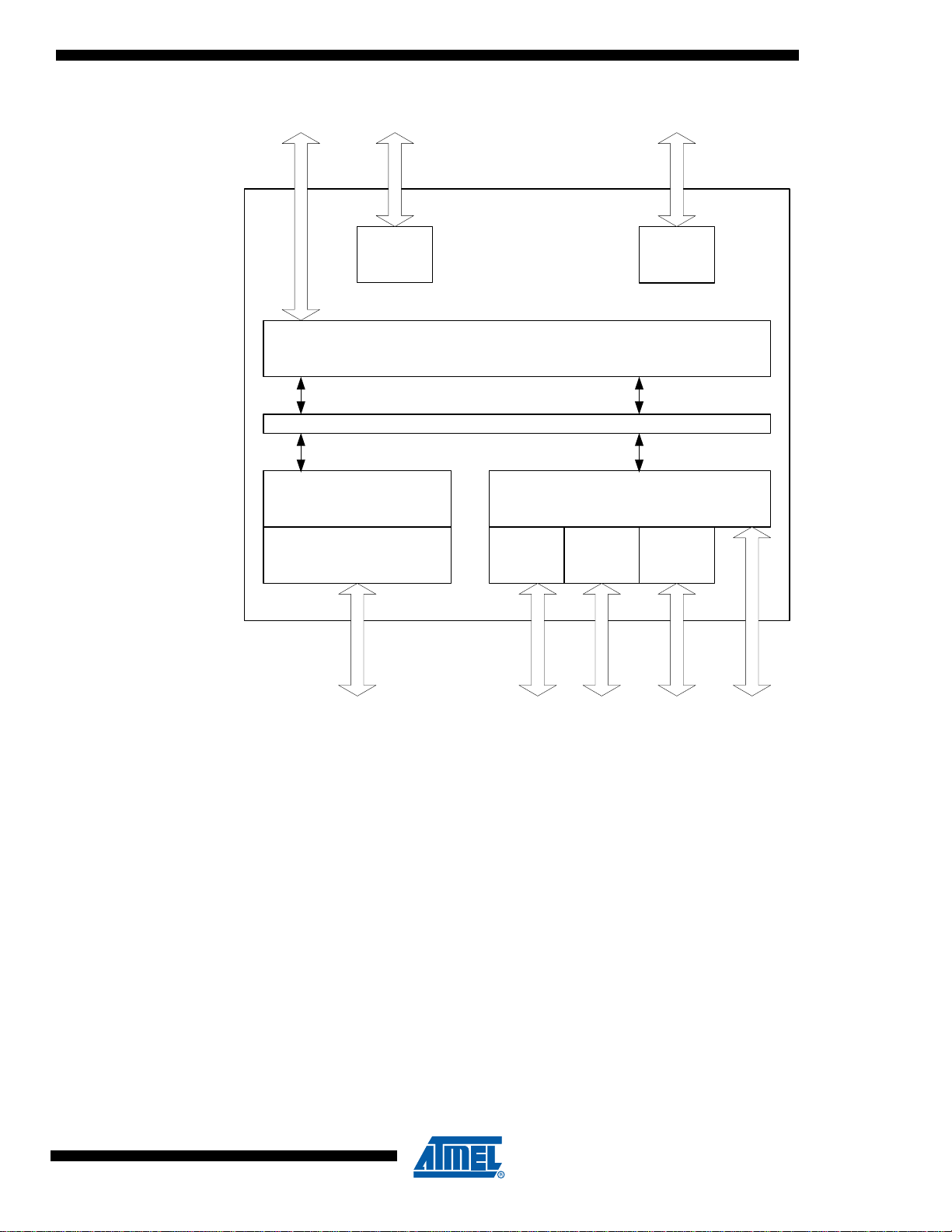

Figure 1-1. Overview of AVR32UC.

1.8 AVR32UC CPU revisions

Three revisions of the AVR32UC CPU currently exist:

• Revision 1 implementing revision 1 of the AVR32 architecture.

• Revision 2 implementing revision 2 of the AVR32 architecture, and with a faster divider.

• Revision 3 implementing revision 3 of the AVR32 architecture, and with optional floating-point

hardware.

Revision 2 of the AVR32UC CPU added the following instructions:

• movh Rd, imm

• {add, sub, and, or, eor}{cond4}, Rd, Rx, Ry

• ld.{sb, ub, sh, uh, w}{cond4} Rd, Rp[disp]

• st.{b, h, w}{cond4} Rp[disp], Rs

• rsub{cond4} Rd, imm

Revision 3 of the AVR32UC CPU added the following instructions:

AVR32UC CPU pipeline

Instruction memory controller Data memory controller

High

Speed

Bus

master

MPU

High Speed Bus

High Speed Bus

OCD

system

OCD interface

Interrupt controller interface

High

Speed

Bus slave

High Speed Bus

Data RAM interface

High Speed Bus master

Power/

Reset

control

Reset interface

CPU Local

Bus

master

CPU Local Bus

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件