Datasheet 搜索 > DA转换器 > ADI(亚德诺) > AD9832BRU 数据手册 > AD9832BRU 用户编程技术手册 5/29 页

器件3D模型

器件3D模型¥ 63.149

AD9832BRU 用户编程技术手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

DA转换器

封装:

TSSOP-16

描述:

CMOS DDS完成 CMOS Complete DDS

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

AD9832BRU数据手册

Page:

of 29 Go

若手册格式错乱,请下载阅览PDF原文件

Data Sheet AD9832

Rev. E | Page 5 of 28

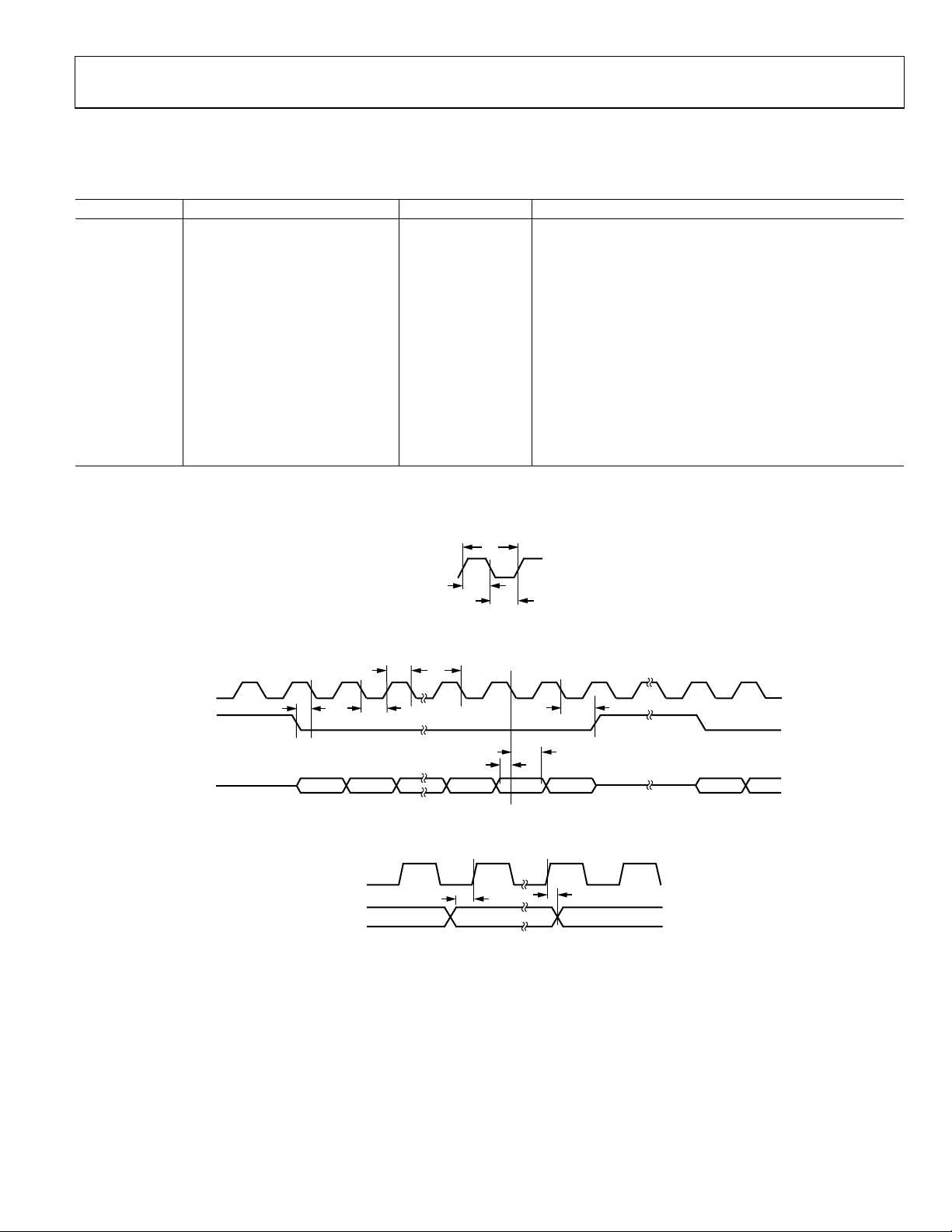

TIMING CHARACTERISTICS

V

DD

= +5 V ± 5%; AGND = DGND = 0 V, unless otherwise noted.

Table 2.

Parameter Limit at T

MIN

to T

MAX

(B Version) Unit Test Conditions/Comments

t

1

40 ns min MCLK period

t

2

16 ns min MCLK high duration

t

3

16 ns min MCLK low duration

t

4

50 ns min SCLK period

t

5

20 ns min SCLK high duration

t

6

20 ns min SCLK low duration

t

7

15 ns min FSYNC to SCLK falling edge setup time

t

8

20 ns min FSYNC to SCLK hold time

SCLK − 5 ns max

t

9

15 ns min Data setup time

t

10

5 ns min Data hold time

t

11

8 ns min FSELECT, PSEL0, PSEL1 setup time before MCLK rising edge

t

11A

1

8 ns min FSELECT, PSEL0, PSEL1 setup time after MCLK rising edge

1

See the Pin Configuration and Function Descriptions section.

Timing Diagrams

MCLK

t

2

t

1

t

3

09090-003

Figure 3. Master Clock

SCLK

FSYNC

SDATA

t

5

t

4

t

6

t

7

t

8

t

10

t

9

D14D15D0D1D2D15 D14

09090-004

Figure 4. Serial Timing

t

11A

t

11

VALID DATA

VALID DATA VALID DATA

MCLK

FSELECT

PSEL0, PSEL1

09090-005

Figure 5. Control Timing

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件