Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > EP1C20F400C8 数据手册 > EP1C20F400C8 用户编程技术手册 5/128 页

器件3D模型

器件3D模型¥ 110.381

EP1C20F400C8 用户编程技术手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

FBGA-400

描述:

可编程逻辑器件(CPLD/FPGA) EP1C20F400C8 FBGA-400

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

EP1C20F400C8数据手册

Page:

of 128 Go

若手册格式错乱,请下载阅览PDF原文件

Altera Corporation 5

FLEX 10K Embedded Programmable Logic Device Family Data Sheet

Notes to tables:

(1) FLEX 10K and FLEX 10KA device package types include plastic J-lead chip carrier (PLCC), thin quad flat pack

(TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), ball-grid array (BGA), pin-grid array (PGA),

and FineLine BGA

TM

packages.

(2) This option is supported with a 256-pin FineLine BGA package. By using SameFrame pin migration, all FineLine

BGA packages are pin compatible. For example, a board can be designed to support both 256-pin and 484-pin

FineLine BGA packages. The Altera software automatically avoids conflicting pins when future migration is set.

General

Description

Altera’s FLEX 10K devices are the industry’s first embedded PLDs. Based

on reconfigurable CMOS SRAM elements, the Flexible Logic Element

MatriX (FLEX) architecture incorporates all features necessary to

implement common gate array megafunctions. With up to 250,000 gates,

the FLEX 10K family provides the density, speed, and features to integrate

entire systems, including multiple 32-bit buses, into a single device.

FLEX 10K devices are reconfigurable, which allows 100% testing prior to

shipment. As a result, the designer is not required to generate test vectors

for fault coverage purposes. Additionally, the designer does not need to

manage inventories of different ASIC designs; FLEX 10K devices can be

configured on the board for the specific functionality required.

Table 6 shows FLEX 10K performance for some common designs. All

performance values were obtained with Synopsys DesignWare or LPM

functions. No special design technique was required to implement the

applications; the designer simply inferred or instantiated a function in a

Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or

schematic design file.

Notes:

(1) The speed grade of this application is limited because of clock high and low specifications.

(2) This application uses combinatorial inputs and outputs.

(3) This application uses registered inputs and outputs.

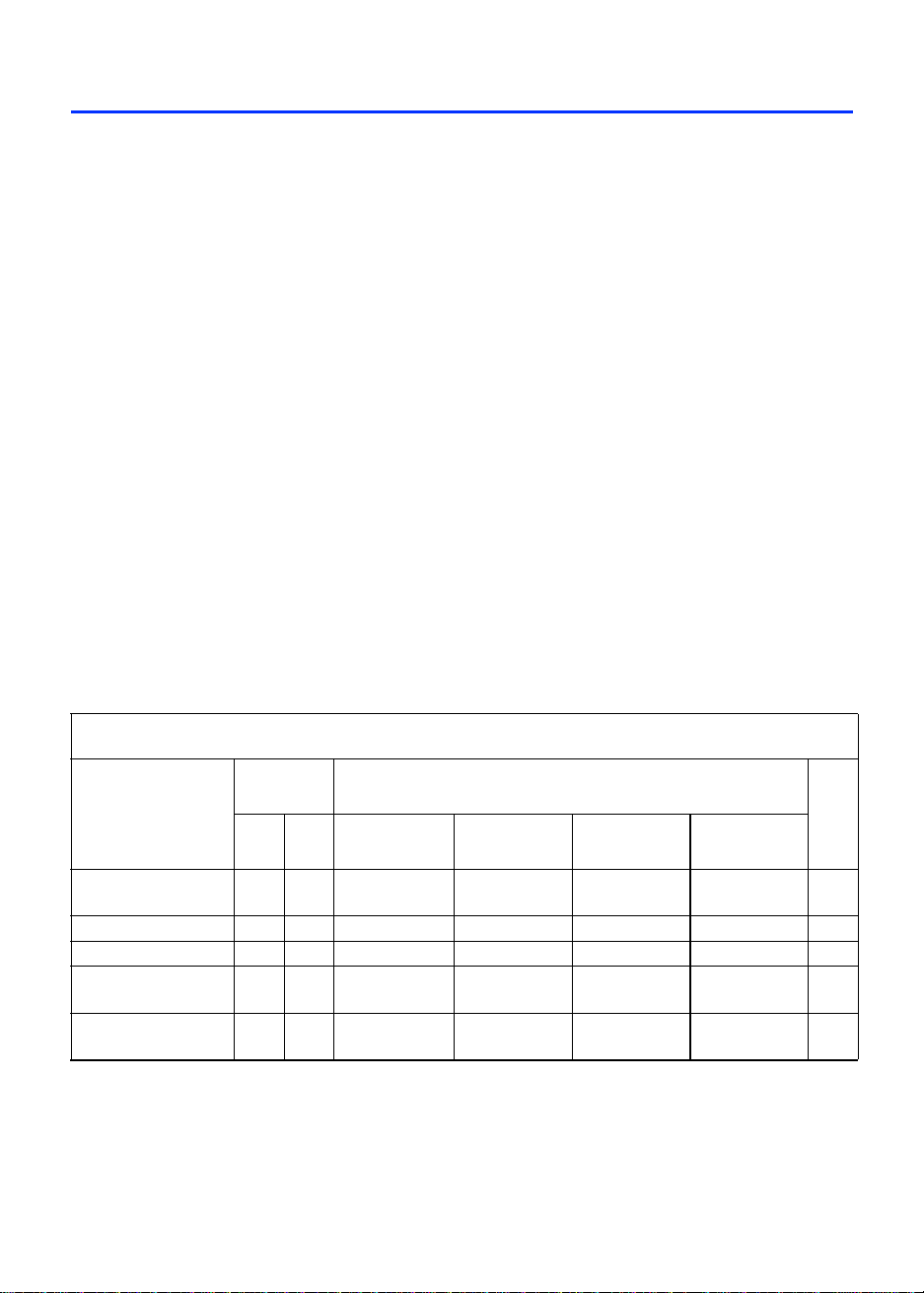

Table 6. FLEX 10K & FLEX 10KA Performance

Application Resources

Used

Performance Units

LEs EABs -1 Speed

Grade

-2 Speed

Grade

-3 Speed

Grade

-4 Speed

Grade

16-bit loadable

counter (1)

16 0 204 166 125 95 MHz

16-bit accumulator (1) 16 0 204 166 125 95 MHz

16-to-1 multiplexer (2) 10 0 4.2 5.8 6.0 7.0 ns

256 × 8 RAM read

cycle speed (3)

0 1 172 145 108 84 MHz

256 × 8 RAM write

cycle speed (3)

01 106 89 68 63 MHz

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件