Datasheet 搜索 > NXP(恩智浦) > MMPF0100F0AZESR2 数据手册 > MMPF0100F0AZESR2 用户编程技术手册 1/153 页

器件3D模型

器件3D模型¥ 46.57

MMPF0100F0AZESR2 用户编程技术手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

封装:

QFN-56

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P7P8P9P10P24Hot

典型应用电路图在P133P134P135P136P137P138P139P140P141

原理图在P6P18P28P43P44P45P59P68P69P70P81P92

封装尺寸在P142

焊盘布局在P140

封装信息在P4P142P143P144P145P146P147P148

功能描述在P17P18P19

技术参数、封装参数在P1P11P13P26P27P29P50P63P76P85P90P91

应用领域在P1P5P133P134P135P136P137P138P139P140P141

电气规格在P13P14P15P16P27P29P50P51P52P53P54P63

型号编号列表在P11

导航目录

MMPF0100F0AZESR2数据手册

Page:

of 153 Go

若手册格式错乱,请下载阅览PDF原文件

Document Number: MMPF0100

Rev. 12.0, 9/2015

Freescale Semiconductor

Advance Information

* This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2012-2015. All rights reserved.

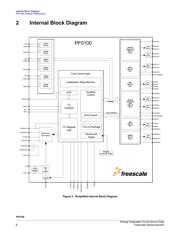

14 Channel Configurable Power

Management Integrated Circuit

The PF0100 SMARTMOS Power Management Integrated Circuit

(PMIC) provides a highly programmable/ configurable architecture,

with fully integrated power devices and minimal external components.

With up to six buck converters, six linear regulators, RTC supply, and

coin-cell charger, the PF0100 can provide power for a complete

system, including applications processors, memory, and system

peripherals, in a wide range of applications. With on-chip One Time

Programmable (OTP) memory, the PF0100 is available in pre-

programmed standard versions, or non-programmed to support

custom programming. The PF0100 is defined to power an entire

embedded MCU platform solution such as i.MX 6 based eReader,

IPTV, medical monitoring, and home/factory automation.

Features:

• Four to six buck converters, depending on configuration

• Single/Dual phase/ parallel options

• DDR termination tracking mode option

• Boost regulator to 5.0 V output

• Six general purpose linear regulators

• Programmable output voltage, sequence, and timing

• OTP (One Time Programmable) memory for device configuration

• Coin cell charger and RTC supply

• DDR termination reference voltage

• Power control logic with processor interface and event detection

•I

2

C control

• Individually programmable ON, OFF, and Standby modes

Figure 1. Simplified Application Diagram

POWER MANAGEMENT

PF0100

Applications:

• Tablets

•IPTV

• eReaders

• Set Top Boxes

• Industrial control

• Medical monitoring

• Home automation/ alarm/ energy management

EP SUFFIX (E-TYPE)

98ASA00405D

56 QFN 8X8

ES SUFFIX (WF-TYPE)

98ASA00589D

56 QFN 8X8

VGEN3

100 mA

VGEN5

100 mA

Camera

Audio

Codec

Cluster/HUD

External AMP

Microphones

Speakers

Front USB

POD

Rear USB

POD

Rear Seat

Infotaiment

Sensors

i.MX 6X

I

2

C Communication

I

2

C Communication

PF0100

Control Signals

Parallel control/GPIOS

LICELL

Charger

COINCELL

Main Supply

2.8 – 4.5 V

VGEN1

100 mA

VGEN2

250 mA

VGEN4

350 mA

VGEN6

200 mA

SWBST

600 mA

SW3A/B

2500 mA

SW1C

2000 mA

SW1A/B

2500 mA

SW2

2000 mA

SW4

1000 mA

GPS

MIPI

uPCIe

SATA - FLASH

NAND - NOR

Interfaces

Processor Core

Voltages

Camera

VREFDDR

DDR Memory

DDR MEMORY

INTERFACE

SD-MMC/

NAND Mem.

SATA

HDD

WAM

GPS

MIPI

HDMI

LDVS Display

USB

Ethernet

CAN

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件