Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F252-I/SP 数据手册 > PIC18F252-I/SP 用户编程技术手册 3/36 页

器件3D模型

器件3D模型¥ 51.954

PIC18F252-I/SP 用户编程技术手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

DIP-28

描述:

MICROCHIP PIC18F252-I/SP 微控制器, 8位, 闪存, PIC18Fxx2, 40 MHz, 32 KB, 1.5 KB, 28 引脚, NDIP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P1P2Hot

导航目录

PIC18F252-I/SP数据手册

Page:

of 36 Go

若手册格式错乱,请下载阅览PDF原文件

2010 Microchip Technology Inc. DS39576C-page 3

PIC18FXX2/XX8

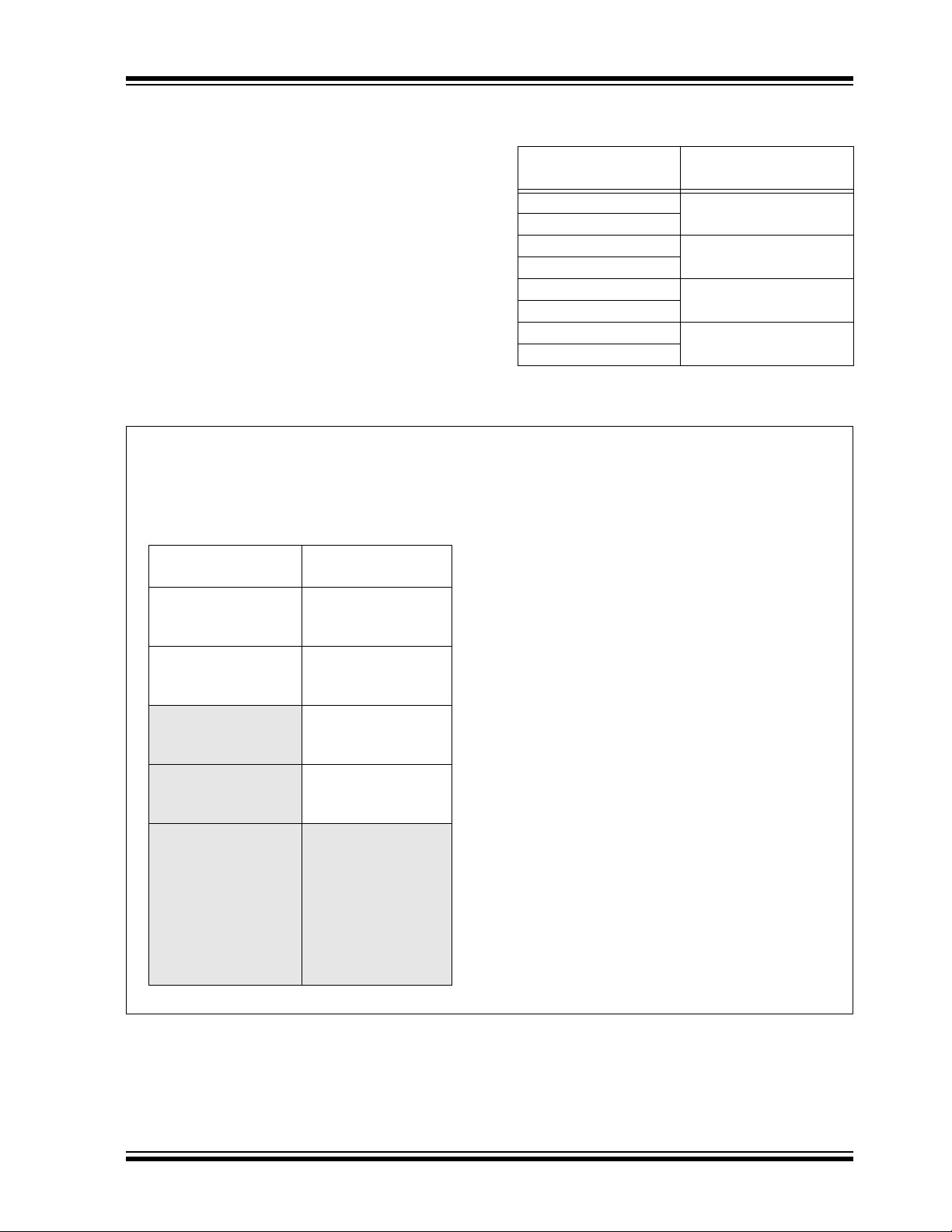

2.3 Memory Map

The code memory space extends from 0000h to 7FFFh

(32 Kbytes) in four, 8-Kbyte panels. Addresses 0000h

through 01FFh, however, define a “Boot Block” region

that is treated separately from Panel 1. All code

memory is on-chip.

In addition to the code memory space, there are three

blocks in the configuration and ID space that are acces-

sible to the user through Table Reads and Table Writes.

Their locations in the memory map are shown in

Figure 2-3.

TABLE 2-2: IMPLEMENTATION OF CODE

MEMORY

FIGURE 2-2: CODE MEMORY SPACE FOR PIC18FXX2/XX8 DEVICES

Device

Code Memory Size

(Bytes)

PIC18F242

0000h - 3FFFh (16K)

PIC18F248

PIC18F252

0000h - 7FFFh (32K)

PIC18F258

PIC18F442

0000h - 3FFFh (16K)

PIC18F448

PIC18F452

0000h - 7FFFh (32K)

PIC18F458

MEMORY SIZE / DEVICE

Block Code Protection

Controlled By:

16 Kbytes

(PIC18FX42)

32 Kbytes

(PIC18FX52)

Address

Range

Boot Block Boot Block

000000h

0001FFh

CPB, WRTB, EBTRB

Block 0 Block 0

000200h

001FFFh

CP0, WRT0, EBTR0

Block 1 Block 1

002000h

003FFFh

CP1, WRT1, EBTR1

Unimplemented

Read ‘0’s

Block 2

004000h

005FFFh

CP2, WRT2, EBTR2

Unimplemented

Read ‘0’s

Block 3

006000h

007FFFh

CP3, WRT3, EBTR3

Unimplemented

Read ‘0’s

Unimplemented

Read ‘0’s

008000h

1FFFFFh

(Unimplemented Memory Space)

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件