Datasheet 搜索 > 微控制器 > ATMEL(爱特美尔) > AT91SAM7S64C-MU 数据手册 > AT91SAM7S64C-MU 开发手册 4/11 页

器件3D模型

器件3D模型¥ 8.436

AT91SAM7S64C-MU 开发手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

微控制器

封装:

QFN-64

描述:

AT91 系列 55 MHz 64 kB 闪存 16 kB SRAM 微控制器 - QFN-64

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

应用领域在P1

导航目录

AT91SAM7S64C-MU数据手册

Page:

of 11 Go

若手册格式错乱,请下载阅览PDF原文件

4

6131A–ATARM–04-Mar-05

AT91 ARM Thumb

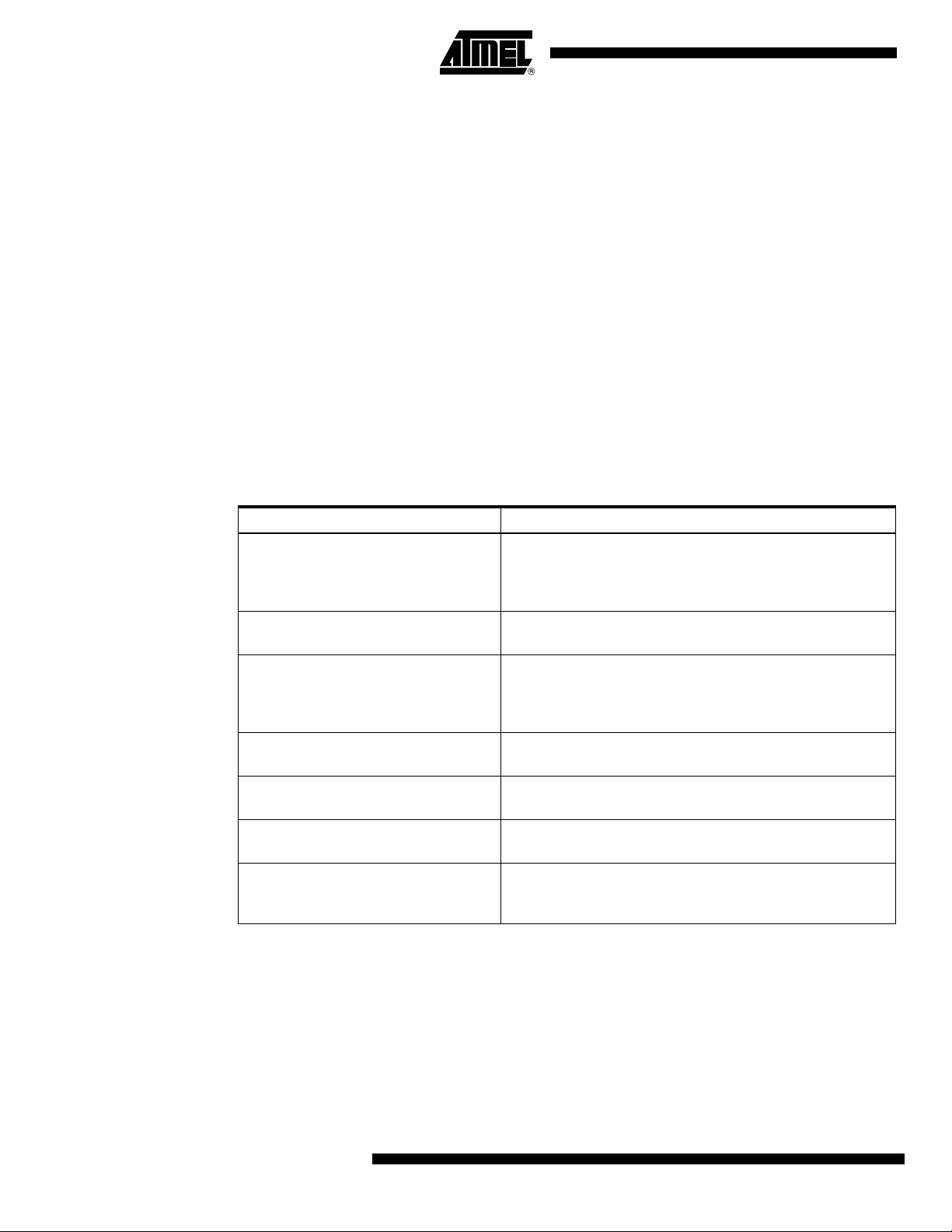

3.2 Setup Exception Vectors

Exception Vectors are setup sequentially through the address space with branches to nearby

labels or branches and links to subroutines. During the normal flow of execution through a pro-

gram, the program counter increases enable the processor to handle events generated by

internal or external sources. Processor exceptions occur when the normal flow of execution is

diverted. Examples of such events are:

• Externally generated interrupts.

• An attempt by the processor to execute an Undefined Instruction.

The previous processor status Is preserved in SPSR. The Link register (R14) and the stack reg-

ister (R13) are also preserved by the hard-coded sequence. When handling such exceptions, so

that execution of the program that was running when the exception occurred can resume when

the appropriate exception routine has completed, the initialization code must set up the required

exception vectors (see Table 3-1).

The Flash is located at address 0x0 and the vectors consist of a sequence of hard-coded

instructions to branch to the handler for each exception. These vectors are mapped at address

0x0....

Processor exception handling is controlled by a vector table. The vector table is a reserved area

of 32 bytes, usually at the bottom of the memory map. It has one word of space allocated to

each exception type, and one word that is currently reserved. Because there is not enough

space to contain the full code for a handler except for the FIQ interrupt, the vector entry for each

exception type contains a branch instruction or load pc instruction to continue execution with the

appropriate handler.The FIQ exception handler can be written directly at the exception vector.

Table 3-1. Exception Vectors

Exception Description

Reset Occurs when the processor reset pin is asserted. This

exception is only expected to occur for signalling power-up,

or for resetting. A soft reset can be done by branching to the

reset vector.

Undefined Instruction Occurs if neither the processor, or any attached coprocessor,

recognizes the currently executing instruction.

Software Interrupt (SWI) This is a user-defined synchronous interrupt instruction. It

allows a program running in User Mode, for example, to

request privileged operations that run in Supervisor Mode,

such as an RTOS function.

Prefetch Abort Occurs when the processor attempts to execute an

instruction that has prefetched from an illegal address.

Data Abort Occurs when a data transfer instruction attempts to load or

store data at an illegal address.

IRQ Occurs when the processor external interrupt request pin is

asserted (LOW) and the I bit in the CPSR is clear.

FIQ Occurs when the processor external fast interrupt request pin

is asserted (LOW) and the F bit in the CPSR is clear or when

an internal interrupt is redirected by Fast Forcing.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件