Datasheet 搜索 > 存储芯片 > Microchip(微芯) > 24AA01T-I/ST 数据手册 > 24AA01T-I/ST 其他数据使用手册 4/47 页

器件3D模型

器件3D模型¥ 2.481

24AA01T-I/ST 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

存储芯片

封装:

TSSOP-8

描述:

8 TSSOP 4.4mm 1K 128x8 卷盘

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

24AA01T-I/ST数据手册

Page:

of 47 Go

若手册格式错乱,请下载阅览PDF原文件

2009-2021 Microchip Technology Inc. DS20001711M-page 4

24AA01/24LC01B/24FC01

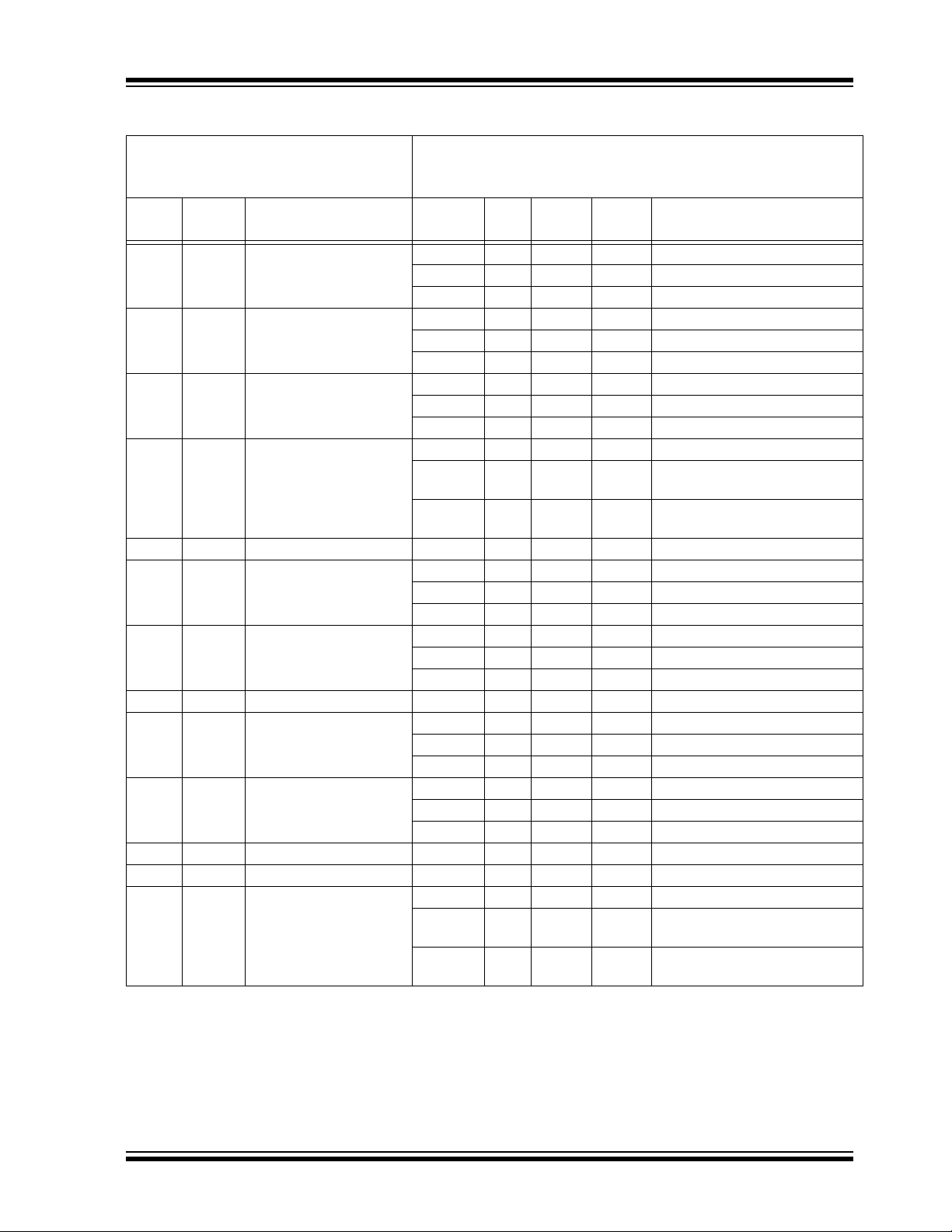

TABLE 1-2 AC CHARACTERISTICS

AC CHARACTERISTICS

Industrial (I): T

A = -40°C to +85°C, VCC = +1.7V to +5.5V

Extended (E): T

A = -40°C to +125°C, VCC = +2.5V to +5.5V (24LC01B)

Extended (E): T

A = -40°C to +125°C, VCC = +1.7V to +5.5V (24FC01)

Param.

No.

Symbol Characteristic Min. Typ. Max. Units Conditions

1F

CLK Clock Frequency — — 400 kHz 2.5V ≤ VCC ≤ 5.5V

— — 100 kHz 1.7V ≤ VCC < 2.5V (24AA01)

— — 1000 kHz 1.7V ≤ VCC ≤ 5.5V (24FC01)

2T

HIGH Clock High Time 600 — — ns 2.5V ≤ VCC ≤ 5.5V

4000 — — ns 1.7V ≤ VCC < 2.5V (24AA01)

260 — — ns 1.7V ≤ VCC ≤ 5.5V (24FC01)

3T

LOW Clock Low Time 1300 — — ns 2.5V ≤ VCC ≤ 5.5V

4700 — — ns 1.7V ≤ VCC < 2.5V (24AA01)

500 — — ns 1.7V ≤ VCC ≤ 5.5V (24FC01)

4T

R SDA and SCL Rise Time — — 300 ns 2.5V ≤ VCC ≤ 5.5V (Note 1)

— — 1000 ns 1.7V ≤ VCC < 2.5V (24AA01)

(Note 1)

— — 1000 ns 1.7V ≤ V

CC ≤ 5.5V (24FC01)

(Note 1)

5T

F SDA and SCL Fall Time — — 300 ns (Note 1)

6T

HD:STA Start Condition Hold Time 600 — — ns 2.5V ≤ VCC ≤ 5.5V

4000 — — ns 1.7V ≤ VCC < 2.5V (24AA01)

250 — — ns 1.7V ≤ VCC ≤ 5.5V (24FC01)

7T

SU:STA Start Condition Setup

Time

600 — — ns 2.5V ≤ VCC ≤ 5.5V

4700 — — ns 1.7V ≤ VCC < 2.5V (24AA01)

250 — — ns 1.7V ≤ VCC ≤ 5.5V (24FC01)

8T

HD:DAT Data Input Hold Time 0 — — ns (Note 2)

9TSU:DAT Data Input Setup Time 100 — — ns 2.5V ≤ VCC ≤ 5.5V

250 — — ns 1.7V ≤ VCC < 2.5V (24AA01)

50 — — ns 1.7V ≤ V

CC ≤ 5.5V (24FC01)

10 TSU:STO Stop Condition Setup

Time

600 — — ns 2.5V ≤ VCC ≤ 5.5V

4000 — — ns 1.7V ≤ VCC < 2.5V (24AA01)

250 — — ns 1.7V ≤ V

CC ≤ 5.5V (24FC01)

11 TSU:WP WP Setup Time 0 — — ns 1.7V ≤ VCC ≤ 5.5V (24FC01)

12 THD:WP WP Hold Time 1000 — — ns 1.7V ≤ VCC ≤ 5.5V (24FC01)

13 T

AA Output Valid from Clock — — 900 ns 2.5V ≤ VCC ≤ 5.5V (Note 2)

— — 3500 ns 1.7V ≤ VCC < 2.5V (24AA01)

(Note 2)

——450ns1.7V ≤ V

CC ≤ 5.5V (24FC01)

(Note 2)

Note 1: Characterized but not 100% tested.

2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region

(minimum 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

3: C

B = total capacitance of one bus line in pF.

4: This parameter is not tested but ensured by characterization.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件