Datasheet 搜索 > 开发套件 > TI(德州仪器) > ADC08D1000DEV/NOPB 数据手册 > ADC08D1000DEV/NOPB 其他数据使用手册 1/40 页

¥ 35309.273

ADC08D1000DEV/NOPB 其他数据使用手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

开发套件

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

ADC08D1000DEV/NOPB数据手册

Page:

of 40 Go

若手册格式错乱,请下载阅览PDF原文件

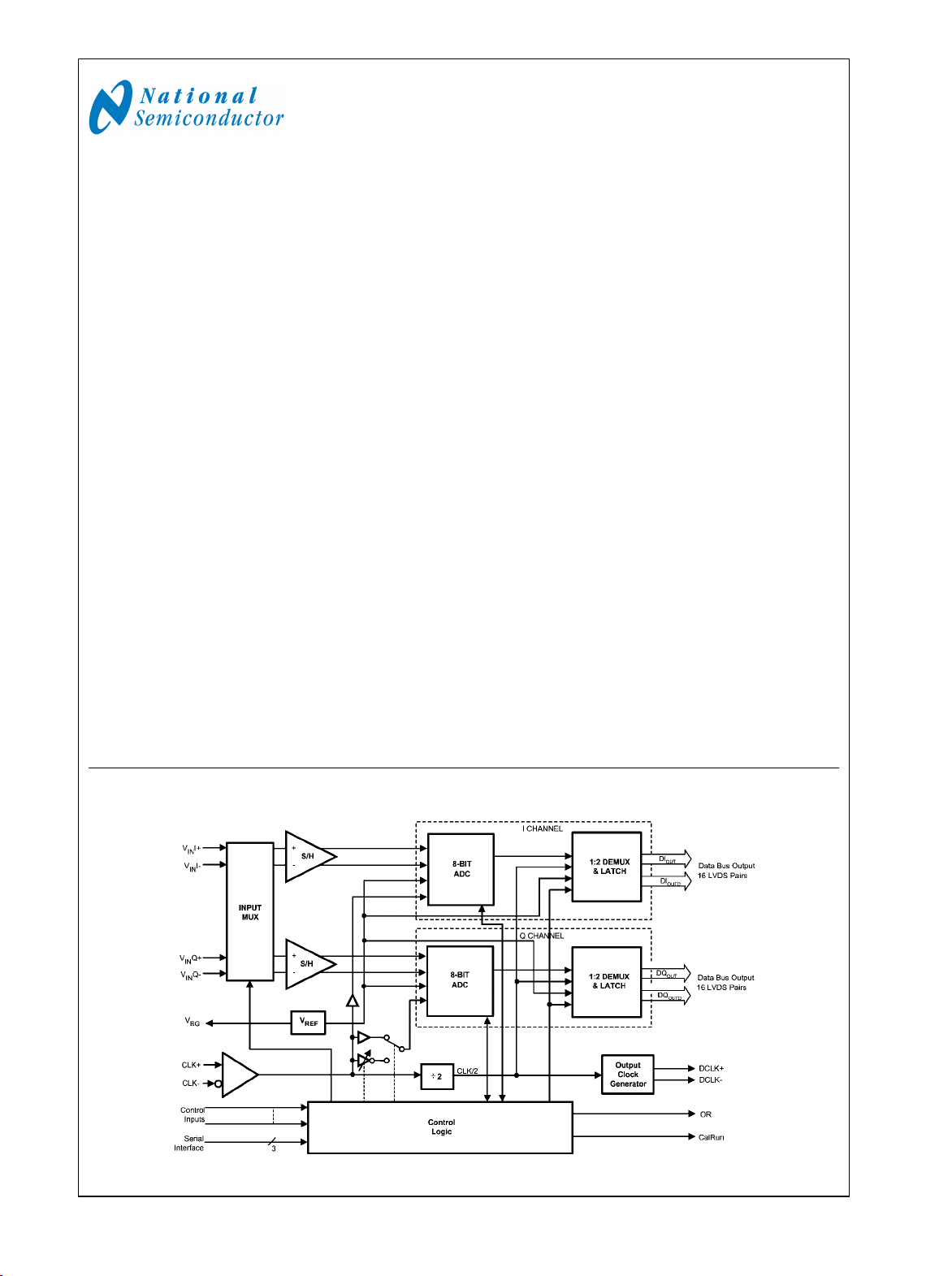

ADC08D1000

April 16, 2009

High Performance, Low Power, Dual 8-Bit, 1 GSPS A/D

Converter

General Description

The ADC08D1000 is a dual, low power, high performance

CMOS analog-to-digital converter that digitizes signals to 8

bits resolution at sampling rates up to 1.3 GSPS. Consuming

a typical 1.6 Watts at 1 GSPS from a single 1.9 Volt supply,

this device is guaranteed to have no missing codes over the

full operating temperature range. The unique folding and in-

terpolating architecture, the fully differential comparator de-

sign, the innovative design of the internal sample-and-hold

amplifier and the self-calibration scheme enable a very flat

response of all dynamic parameters beyond Nyquist, produc-

ing a high 7.4 ENOB with a 500 MHz input signal and a 1 GHz

sample rate while providing a 10

-18

B.E.R. Output formatting

is offset binary and the LVDS digital outputs are compatible

with IEEE 1596.3-1996, with the exception of an adjustable

common mode voltage between 0.8V and 1.2V.

Each converter has a 1:2 demultiplexer that feeds two LVDS

buses and reduces the output data rate on each bus to half

the sampling rate. The two converters can be interleaved and

used as a single 2 GSPS ADC.

The converter typically consumes less than 3.5 mW in the

Power Down Mode and is available in a 128-lead, thermally

enhanced exposed pad LQFP and operates over the Indus-

trial (-40°C ≤ T

A

≤ +85°C) temperature range.

Features

■

Internal Sample-and-Hold

■

Single +1.9V ±0.1V Operation

■

Choice of SDR or DDR output clocking

■

Interleave Mode for 2x Sampling Rate

■

Multiple ADC Synchronization Capability

■

Guaranteed No Missing Codes

■

Serial Interface for Extended Control

■

Fine Adjustment of Input Full-Scale Range and Offset

■

Duty Cycle Corrected Sample Clock

Key Specifications

■

Resolution 8 Bits

■

Max Conversion Rate 1 GSPS (min)

■

Bit Error Rate 10

-18

(typ)

■

ENOB @ 500 MHz Input 7.4 Bits (typ)

■

DNL ±0.15 LSB (typ)

■

Power Consumption

■

—

Operating 1.6 W (typ)

—

Power Down Mode 3.5 mW (typ)

Applications

■

Direct RF Down Conversion

■

Digital Oscilloscopes

■

Satellite Set-top boxes

■

Communications Systems

■

Test Instrumentation

Block Diagram

20097453

© 2009 National Semiconductor Corporation 200974 www.national.com

ADC08D1000 High Performance, Low Power, Dual 8-Bit, 1 GSPS A/D Converter

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件