Datasheet 搜索 > 逻辑控制器 > ON Semiconductor(安森美) > MC100EPT21MNR4 数据手册 > MC100EPT21MNR4 其他数据使用手册 4/11 页

¥ 0

MC100EPT21MNR4 其他数据使用手册 - ON Semiconductor(安森美)

制造商:

ON Semiconductor(安森美)

分类:

逻辑控制器

封装:

VFDFN-8

描述:

3.3V差分LVPECL / LVDS / CML到LVTTL / LVCMOS翻译 3.3V Differential LVPECL/LVDS/CML to LVTTL/LVCMOS Translator

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

MC100EPT21MNR4数据手册

Page:

of 11 Go

若手册格式错乱,请下载阅览PDF原文件

MC100EPT21

http://onsemi.com

4

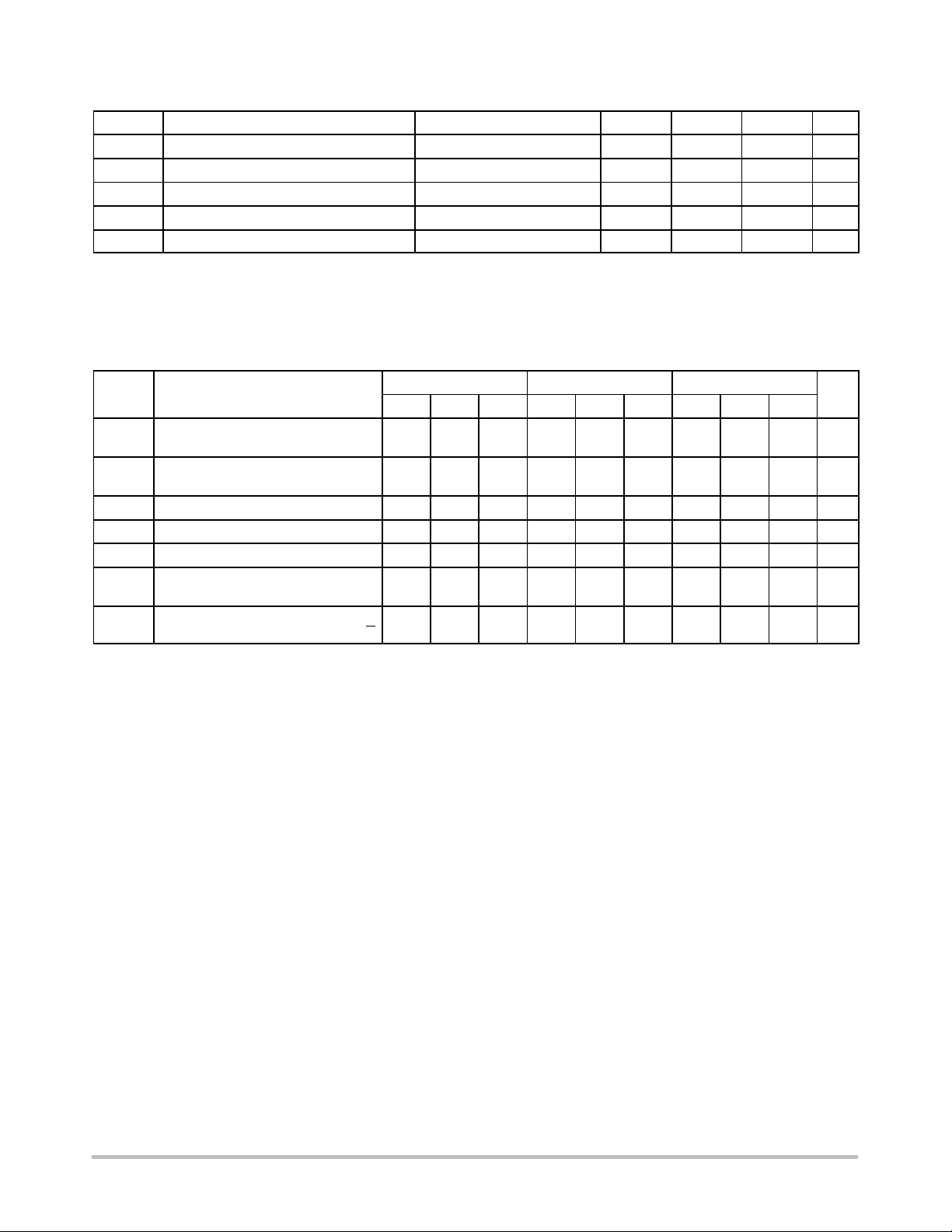

Table 5. LVTTL/LVCMOS OUTPUT DC CHARACTERISTICS V

CC

= 3.3 V, GND = 0.0 V, T

A

= −40°C to 85°C

Symbol Characteristic Condition Min Typ Max Unit

V

OH

Output HIGH Voltage I

OH

= −3.0 mA 2.4 V

V

OL

Output LOW Voltage I

OL

= 24 mA 0.5 V

I

CCH

Power Supply Current Outputs set to HIGH 5 17 25 mA

I

CCL

Power Supply Current Outputs set to LOW 8 21 30 mA

I

OS

Output Short Circuit Current −130 −80 mA

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared

operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit

values are applied individually under normal operating conditions and not valid simultaneously.

Table 6. AC CHARACTERISTICS V

CC

= 3.0 V to 3.6 V, GND = 0.0 V (Note 5)

Symbol Characteristic

−40°C 25°C 85°C

Unit

Min Typ Max Min Typ Max Min Typ Max

f

max

Maximum Frequency

(Figure 2) 275 350 275 350 275 350

MHz

t

PLH

,

t

PHL

Propagation Delay to

Output Differential

800

1200

1400

1400

2050

1800

800

1200

1400

1400

2250

1800

900

1100

1600

1300

2950

1900

ps

t

SKEW

Duty Cycle Skew (Note 6) 45 50 55 45 50 55 45 50 55 %

t

SKPP

Part−to−Part Skew (Note 6) 500 500 500 ps

t

JITTER

Random Clock Jitter (RMS) 3.5 5 3.5 5 3.5 5 ps

V

PP

Input Voltage Swing

(Differential Configuration)

150 800 1200 150 800 1200 150 800 1200 mV

t

r

t

f

Output Rise/Fall Times

(0.8V − 2.0V) Q, Q 250 600 900 250 600 900 250 600 900

ps

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared

operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit

values are applied individually under normal operating conditions and not valid simultaneously.

5. Measured with a 750 mV 50% duty−cycle clock source. R

L

= 500 W to GND and C

L

= 20 pF to GND. Refer to FIgure 3.

6. Skews are measured between outputs under identical transitions. Duty cycle skew is measured between differential outputs using the

deviations of the sum Tpw− and Tpw+.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件