Datasheet 搜索 > ON Semiconductor(安森美) > NCP4305DDR2G 数据手册 > NCP4305DDR2G 其他数据使用手册 6/54 页

器件3D模型

器件3D模型¥ 4.169

NCP4305DDR2G 其他数据使用手册 - ON Semiconductor(安森美)

制造商:

ON Semiconductor(安森美)

封装:

SOIC-8

描述:

SMPS拓扑

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

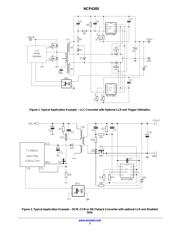

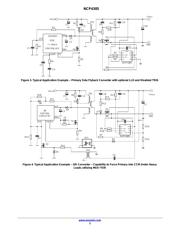

典型应用电路图在P1P2P3P35

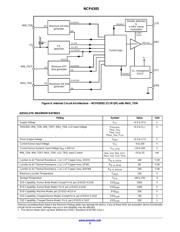

原理图在P48

封装尺寸在P50P51P52

焊盘布局在P50P51P52

型号编码规则在P1P49P54

标记信息在P1P49P50P51P52P54

封装信息在P49

功能描述在P4P15

技术参数、封装参数在P5P49

应用领域在P1

电气规格在P6P7

型号编号列表在P5

导航目录

NCP4305DDR2G数据手册

Page:

of 54 Go

若手册格式错乱,请下载阅览PDF原文件

NCP4305

www.onsemi.com

6

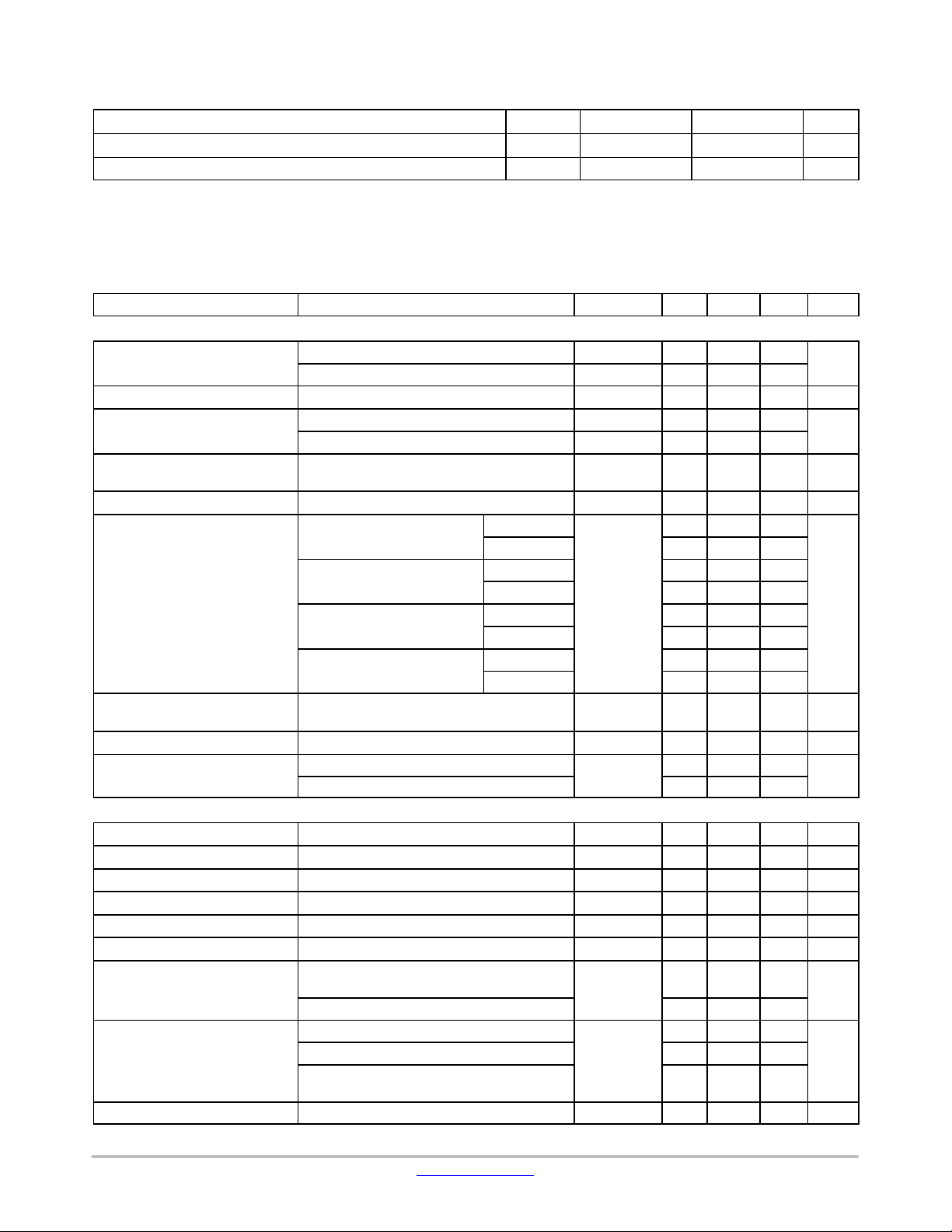

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Min Max Unit

Maximum Operating Input Voltage V

CC

35 V

Operating Junction Temperature T

J

−40 125 °C

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond

the Recommended Operating Ranges limits may affect device reliability.

ELECTRICAL CHARACTERISTICS

−40°C ≤ T

J

≤ 125°C; V

CC

= 12 V; C

DRV

= 0 nF; R

MIN_TON

= R

MIN_TOFF

= 10 kW; V

TRIG/DIS

= 0 V; V

LLD

= 0 V; V

CS

= −1 to +4 V; f

CS

=

100 kHz, DC

CS

= 50%, unless otherwise noted. Typical values are at T

J

= +25°C

Parameter

Test Conditions Symbol Min Typ Max Unit

SUPPLY SECTION

VCC UVLO (ver. B & C)

V

CC

rising V

CCON

8.3 8.8 9.4

V

V

CC

falling V

CCOFF

7.3 7.8 8.3

VCC UVLO Hysteresis (ver. B & C) V

CCHYS

1.0 V

VCC UVLO (ver. A, D & Q)

V

CC

rising V

CCON

4.20 4.45 4.80

V

V

CC

falling V

CCOFF

3.70 3.95 4.20

VCC UVLO Hysteresis

(ver. A, D & Q)

V

CCHYS

0.5 V

Start−up Delay

V

CC

rising from 0 to V

CCON

+ 1 V @ tr = 10 ms

t

START_DEL

75 125

ms

Current Consumption,

R

MIN_TON

= R

MIN_TOFF

= 0 kW

C

LOAD

= 0 nF, f

SW

= 500 kHz

A, C

I

CC

3.3 4.0 5.6

mA

B, D, Q 3.8 4.5 6.0

C

LOAD

= 0 nF, f

SW

= 500 kHz,

WDFN

A, C 3.0 4.0 5.6

B, D, Q 3.5 4.5 6.0

C

LOAD

= 1 nF, f

SW

= 500 kHz

A, C 4.5 6.0 7.5

B, D, Q 7.7 9.0 10.7

C

LOAD

= 10 nF, f

SW

= 500 kHz

A, C 20 25 30

B, D, Q 40 50 60

Current Consumption No switching, V

CS

= 0 V,

R

MIN_TON

= R

MIN_TOFF

= 0 k

I

CC

1.5 2.0 2.5 mA

Current Consumption below UVLO No switching, V

CC

= V

CCOFF

– 0.1 V, V

CS

= 0 V I

CC_UVLO

75 125

mA

Current Consumption in Disable

Mode

V

LLD

= V

CC

− 0.1 V, V

CS

= 0 V

I

CC_DIS

40 55 70

mA

V

TRIG

= 5 V, V

LLD

= V

CC

– 3 V, V

CS

= 0 V 45 65 80

DRIVER OUTPUT

Output Voltage Rise−Time

C

LOAD

= 10 nF, 10% to 90% V

DRVMAX

t

r

40 55 ns

Output Voltage Fall−Time C

LOAD

= 10 nF, 90% to 10% V

DRVMAX

t

f

20 35 ns

Driver Source Resistance R

DRV_SOURCE

1.2

W

Driver Sink Resistance R

DRV_SINK

0.5

W

Output Peak Source Current I

DRV_SOURCE

4 A

Output Peak Sink Current I

DRV_SINK

8 A

Maximum Driver Output Voltage

V

CC

= 35 V, C

LOAD

> 1 nF, V

LLD

= 0 V,

(ver. B, D and Q)

V

DRVMAX

9.0 9.5 10.5

V

V

CC

= 35 V, C

LOAD

> 1 nF, V

LLD

= 0 V, (ver. A, C) 4.3 4.7 5.5

Minimum Driver Output Voltage

V

CC

= V

CCOFF

+ 200 mV, V

LLD

= 0 V, (ver. B)

V

DRVMIN

7.2 7.8 8.5

V

V

CC

= V

CCOFF

+ 200 mV, V

LLD

= 0 V, (ver. C) 4.2 4.7 5.3

V

CC

= V

CCOFF

+ 200 mV, V

LLD

= 0 V,

(ver. A, D, Q)

3.6 4.0 4.4

Minimum Driver Output Voltage V

LLD

= V

CC

− V

LLDREC

V V

DRVLLDMIN

0.0 0.4 1.2 V

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件