Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F458-I/PT 数据手册 > PIC18F458-I/PT 其他数据使用手册 1/8 页

器件3D模型

器件3D模型¥ 108.49

PIC18F458-I/PT 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP-44

描述:

MICROCHIP PIC18F458-I/PT 微控制器, 8位, 闪存, PIC18F, 40 MHz, 32 KB, 1.5 KB, 44 引脚, TQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

PIC18F458-I/PT数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

© 2006 Microchip Technology Inc. DS80161J-page 1

PIC18FXX8

The PIC18FXX8 Rev. C0 parts you have received

conform functionally to the Device Data Sheet

(DS41159D), except for the anomalies described

below.

The following silicon errata apply only to

PIC18FXX8 devices with these Device/Revision

IDs:

1. Module: Core (Program Memory Space)

Performing table read operations above the user

program memory space (addresses over 1FFFFFh)

may yield erroneous results at the extreme low end

of the device’s rated temperature range (-40°C).

This applies specifically to addresses above

1FFFFFh, including the user ID locations

(200000h-200007h), the configuration bytes

(300000h-30000Dh) and the device ID locations

(3FFFFEh and 3FFFFFh). User program memory

is unaffected.

Work around

Two possible work arounds are presented. Other

solutions may exist.

1. Do not perform table read operations on areas

above the user memory space at -40°C.

2. Insert NOP instructions (specifically, literal

FFFFh) around any table read instructions. The

suggested optimal number is 4 instructions

before and 8 instructions after each table read.

This may vary depending upon the particular

application and should be optimized by the user.

Date Codes that pertain to this issue:

All engineering and production devices.

2. Module: Data EEPROM

When reading the data EEPROM, the contents of

the EEDATA register may be corrupted if the RD

bit (EECON1<0>) is set immediately following a

write to the address byte (EEADR). The actual

contents of the data EEPROM remain unaffected.

Work around

Do not set EEADR immediately before the

execution of a read. Write to EEADR at least one

instruction cycle before setting the RD

bit. The

instruction between the write to EEADR and the

read can be any valid instruction, including a NOP.

Date Codes that pertain to this issue:

All engineering and production devices.

3. Module: A/D (External Voltage Reference)

and Comparator Voltage

Reference

When the external voltage reference, VREF-, is

selected for use with either the A/D or comparator

voltage reference, AV

SS is connected to VREF- in

the comparator module. If V

REF- is a voltage other

than AV

SS (which must be tied externally to VSS),

excessive current will flow into the V

REF- pin.

Work around

If external VREF- is used with a voltage other than

0V, enable the comparator voltage reference by

setting the CVREN bit in the CVRCON register.

This disconnects V

REF- and AVSS within the

comparator module.

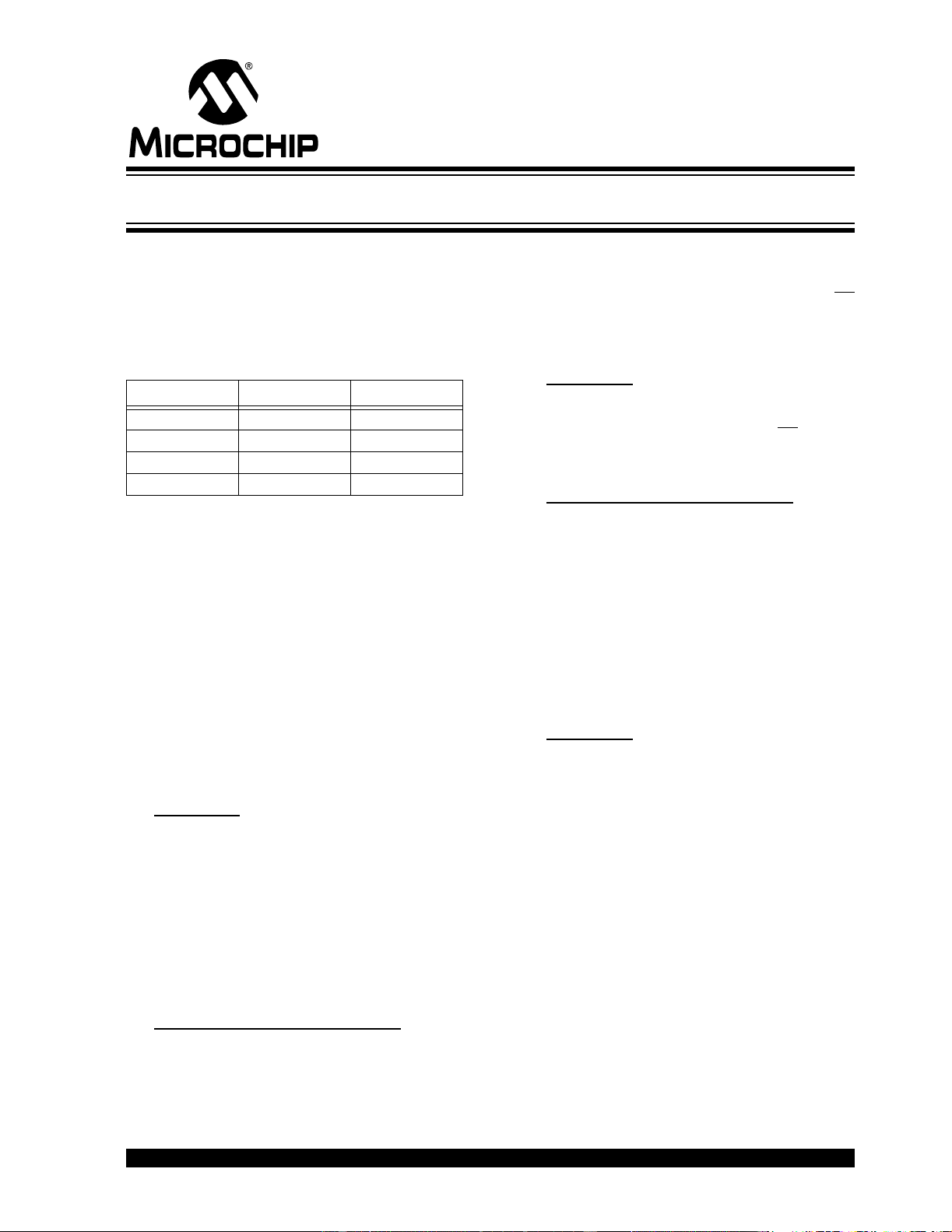

Part Number Device ID Revision ID

PIC18F248 00 1000 000 00101

PIC18F258 00 1000 010 00101

PIC18F448 00 1000 001 00101

PIC18F458 00 1000 011 00101

The Device IDs (DEVID1 and DEVID2) are located at

addresses 3FFFFEh:3FFFFFh in the device’s

configuration space. They are shown in hexadecimal

in the format “DEVID2 DEVID1”.

PIC18FXX8 Rev. C0 Silicon Errata Sheet

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件