Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F45K20-I/P 数据手册 > PIC18F45K20-I/P 其他数据使用手册 2/18 页

器件3D模型

器件3D模型¥ 14.778

PIC18F45K20-I/P 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

PDIP-40

描述:

MICROCHIP PIC18F45K20-I/P 微控制器, 8位, 闪存, AEC-Q100, PIC18FxxKxx, 64 MHz, 32 KB, 1.5 KB, 40 引脚, DIP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

封装信息在P12P13

电气规格在P14

导航目录

PIC18F45K20-I/P数据手册

Page:

of 18 Go

若手册格式错乱,请下载阅览PDF原文件

PIC18F24K20/25K20/44K20/45K20

DS80000425K-page 2 2008-2013 Microchip Technology Inc.

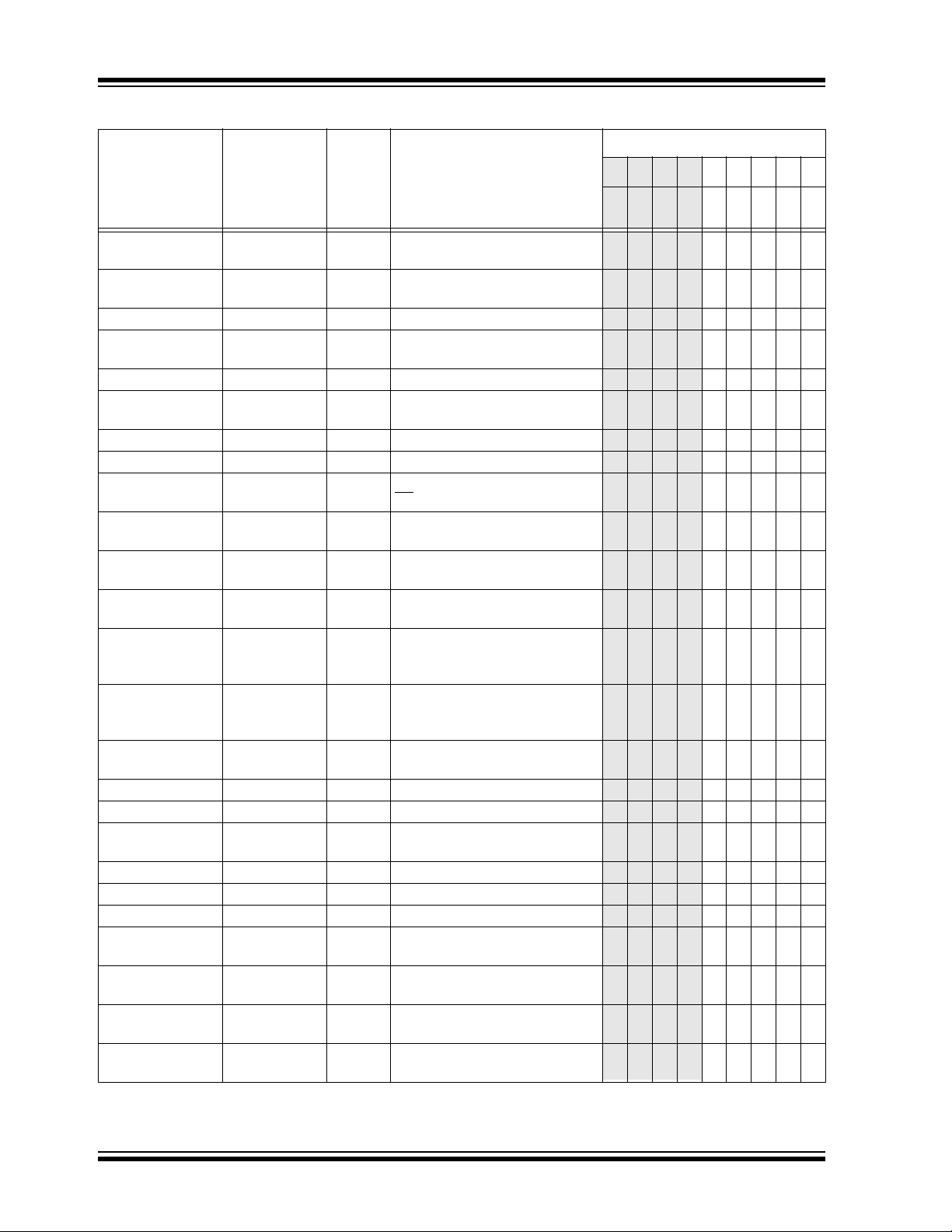

TABLE 2: SILICON ISSUE SUMMARY

Module Feature

Item

Number

Issue Summary

Affected Revisions

(1)

A4

A7

A9

AB

A4

A7

A8

AE

AF

0xA

0xC

0xE

0x11

0x16

0x18

0x19

0x1B

0x1C

ECCP CCP1CON 1. Changing CCP1M bits may

cause capture of Timer1 value.

X X X X

ECCP Full-Bridge

mode

2. Direction change issue.

X X X X

MSSP SPI SPI Clock 3. Shortened SPI high time.

X X X X

MSSP I

2

C™ Slew Rate 4. Slow slew rate when

SLRCON<2> is set.

X X X X

ADC Offset 5. Time dependent on offset.

X X X X

MSSP I

2

C Receiving 6. Address may be received as

data.

X X X X

MSSP I

2

C Master mode 7. Master mode not functional. X

MSSP SPI SPI Master 8. Improper sampling of last bit. X X X X

MSSP SPI SPI Master 9. SSPBUF improperly reloads on

SS

pin transitions.

X X X X

MSSP SPI SPI Master 10. Improper extra pulse on SCK

pin.

X X X X

EUSART Synchronous

Master mode

11. Duty cycle of CK output is

skewed when SPBRG is odd.

X X X X

EUSART Synchronous

Master mode

12. LS bit corruption during

transmission when SPBRG = 3.

X X X X

EUSART Synchronous

Master mode

13. Clock fails to stop at end of

character transmission when

SPBRG = 0.

X X X X

Internal Fixed

Voltage Refer-

ence (FVR)

— 14. FVRST bit activates prematurely. X X

High Low Voltage

Detect (HLVD)

— 15. IVRST bit activates prematurely. X X

BOR FVR 16. Unexpected BOR occurrence. X X

System Clocks — 17. HFINTOSC output accuracy. X X X X

POR/BOR — 18. Unexpected code execution at

low V

DD.

X X X X

POR — 19. Premature POR release.

X X X X

POR — 20. POR may become stuck. X X X X

Clocks EC mode 21. 48 MHz maximum frequency.

X X

Comparators Interrupt-on-

Change

22. Presetting interrupt-on-change

issue.

X X X X

Data EEPROM

Memory

Endurance 23. Endurance is limited to 10K

cycles.

X X X XXXX

Program Flash

Memory

Endurance 24. Endurance is limited to 1K

cycles.

X X X XXXX

Configuration Bits CONFIG3H 25. HFOFST bit erases to ‘0’ instead

of ‘1’.

X X X X

Note 1: Only those issues indicated in the last column apply to the current silicon revision.

2: Shaded cells in this table indicate older device revisions that are no longer in production.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件