Datasheet 搜索 > DSP数字信号处理器 > TI(德州仪器) > TMS320C6748EZCED4 数据手册 > TMS320C6748EZCED4 其他数据使用手册 5/56 页

器件3D模型

器件3D模型¥ 166.507

TMS320C6748EZCED4 其他数据使用手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

DSP数字信号处理器

封装:

LFBGA-361

描述:

低功耗 C674x 浮点 DSP- 456MHz、SATA 361-NFBGA -40 to 90

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

标记信息在P3

封装信息在P3

技术参数、封装参数在P4P5P6P7P9P10P11P12P13P14P15P16

应用领域在P56

导航目录

TMS320C6748EZCED4数据手册

Page:

of 56 Go

若手册格式错乱,请下载阅览PDF原文件

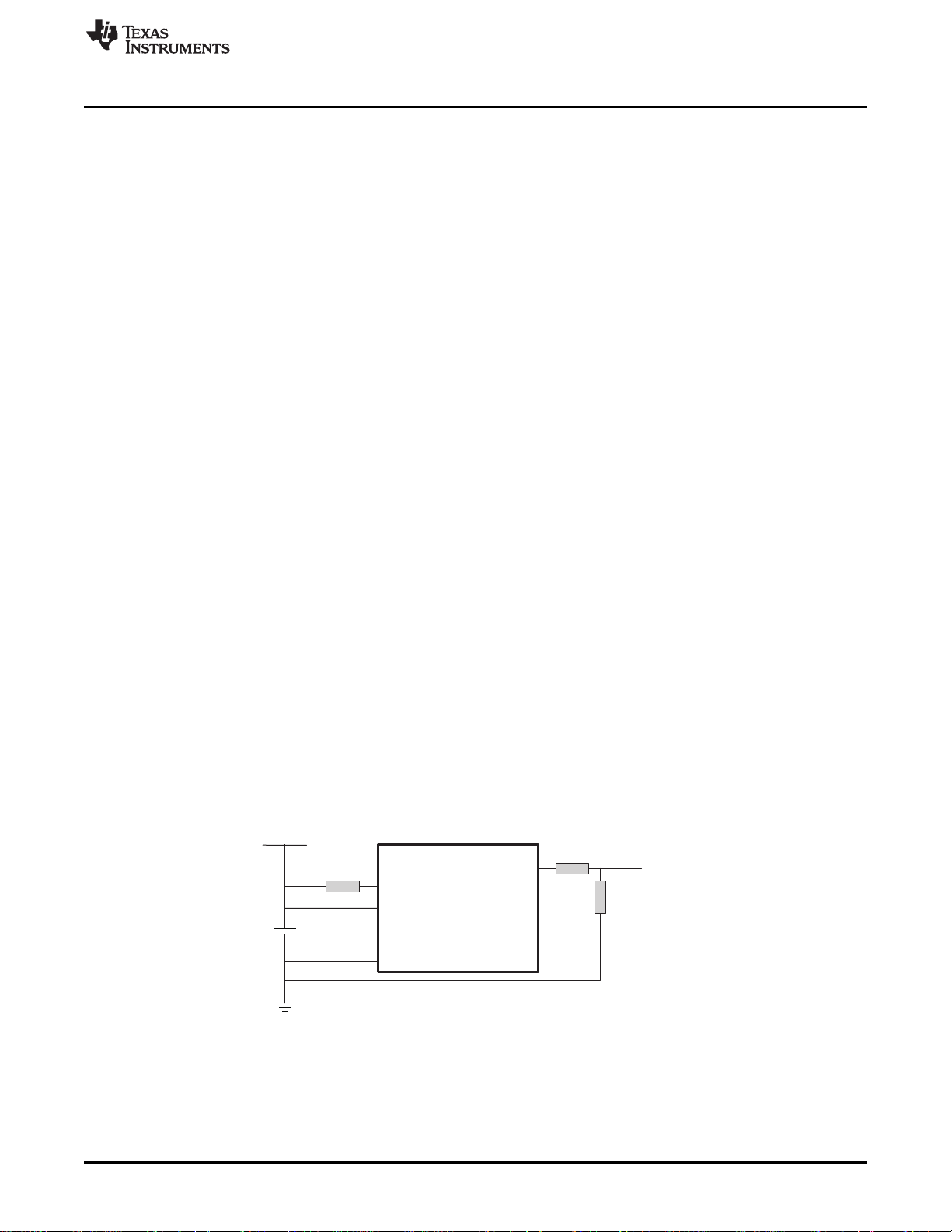

3.3 V

L1

C1

VDD

Enable

GND

OSCOUT

X1

OSCIN

R2

R1

www.ti.com

Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specifications

2.1.3 LCDC: Underflow During Initialization

On all silicon revisions during LCDC initialization, there is the potential for a FIFO underflow condition to

occur. A FIFO underflow condition occurs when the input FIFO is completely empty and the LCDC raster

controller logic that drives data to the output pins attempts to fetch data from the FIFO. When a FIFO

underflow condition occurs, incorrect data will be driven out on the LCDC data pins.

An underflow condition will occur if the DDR2/mDDR Controller issues a refresh command to the SDRAM

memory during LCDC start up/initialization. The error condition will be captured in the LCD Status register

(LCD_STAT) in the FIFO underflow status (FUF) bit field. If the FUF_EN bit is enabled in Raster Control

Register (RASTER_CTRL), the LCDC will send an interrupt to the CPU.

The FIFO underflow described above is not expected to be a common occurrence because of the unlikely

alignment of events required to produce the underflow condition.

The DDR2/mDDR Controller hardware automatically schedules refresh commands to the SDRAM

memory. Therefore, it is not possible for the user/application code to schedule DDR2/mDDR Controller

refresh commands to prevent them from being initiated during LCDC start up. This means that it is not

possible to prevent a DDR2/mDDR Controller refresh occurrence during the start up of the LCDC.

Software should poll the FUF bit field in the LCD_STAT register to check if an error condition has occurred

or service the interrupt if FUF_EN is enabled when FUF occurs. If the FUF bit field has been set to 1, this

will indicate an underflow condition has occurred and then the software should execute a reset of the

LCDC via the LPSC.

This problem may occur if the LCDC FIFO threshold size ( LCDDMA_CTRL[TH_FIFO_READY] ) is left at

its default value after reset. Increasing the FIFO threshold size will reduce or eliminate underflows. Setting

the threshold size to 256 double words or larger is recommended.

2.1.4 System-Level ESD Immunity Usage Note

On all silicon revisions, certain design elements make this device susceptible to radiated noise during an

ESD strike, as described in the standard IEC 61000-4-2. Exposure to the electrical noise caused by the

ESD can cause soft device failures due to noise coupling on the system clock (OSCIN). ESD events within

the IEC spec range do not cause permanent device damage and full functionality is recoverable with a

device reset. The sensitivity to this noise issue is primarily due to the 1.2V oscillator/clock input

implemented on this device. The low voltage range, coupled with slow rise and fall times, provides a lower

noise margin than other TI devices with higher voltage internal oscillators (for example, 1.8V or 3.3V

oscillators).

If ESD robustness is a concern, it is strongly recommended to avoid using the internal oscillator as a clock

source. An external 3.3V clock source with a resistor voltage divider as in Figure 2 can be used to

externally generate the required 1.2V input clock. By using an external clock input with fast rise/fall times

(less than 5 ns), the noise margin improves significantly, increasing ESD noise resistance.

Legend: L1 = ferrite bead; C1 = 0.1 uF; R1 = 165 ohm / 5%; R2 = 100 ohm / 5%

Figure 2. External 3.3V Clock Source

5

SPRZ303H–June 2009–Revised March 2014 TMS320C6748 Fixed- and Floating-Point DSP Silicon Revisions 2.3, 2.1, 2.0,

1.1 and 1.0

Submit Documentation Feedback

Copyright © 2009–2014, Texas Instruments Incorporated

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件