Datasheet 搜索 > DSP数字信号处理器 > TI(德州仪器) > TMS320C6421ZDUQ5 数据手册 > TMS320C6421ZDUQ5 产品设计参考手册 6/222 页

器件3D模型

器件3D模型¥ 45.66

TMS320C6421ZDUQ5 产品设计参考手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

DSP数字信号处理器

封装:

BGA-376

描述:

数字信号处理器和控制器 - DSP, DSC Fixed-Pt Dig Signal Proc

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P16P29P33P74P75P77P79P84P85P86P90P91Hot

原理图在P4P107P108P117P118P166P184

封装尺寸在P218

标记信息在P218P219

封装信息在P217P218P219

技术参数、封装参数在P109P113P114P115P116P117P118P119P120P121P122P123

应用领域在P2P110

电气规格在P106P111P112P113P114P115P116P117P118P119P120P121

导航目录

TMS320C6421ZDUQ5数据手册

Page:

of 222 Go

若手册格式错乱,请下载阅览PDF原文件

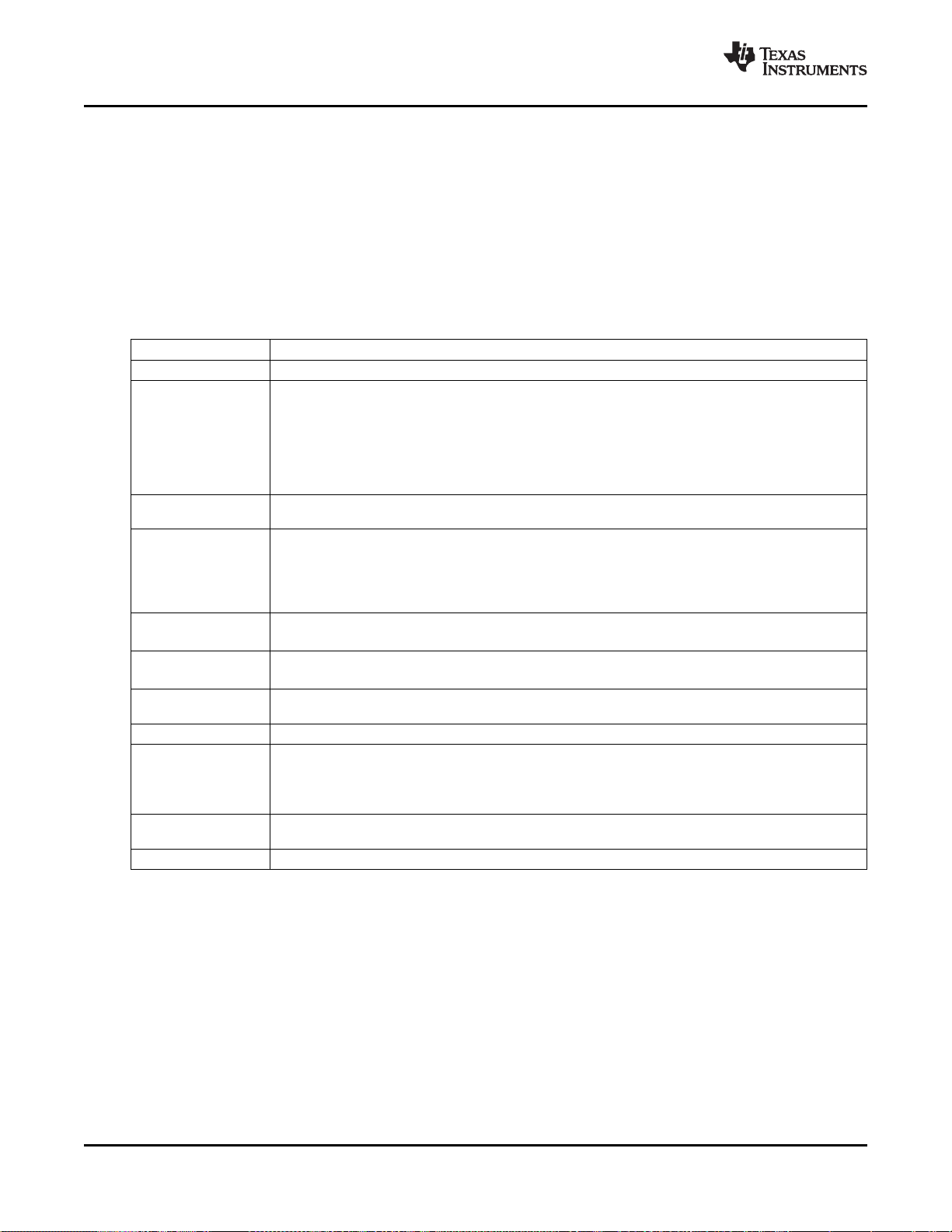

Revision History

TMS320C6421

Fixed-Point Digital Signal Processor

SPRS346D – JANUARY 2007 – REVISED JUNE 2008

www.ti.com

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

This data manual revision history highlights the technical changes made to the SPRS346C device-specific

data manual to make it an SPRS346D revision.

Scope: Applicable updates to the TMS320C642x, specifically relating to the TMS320C6421 device, have

been incorporated.

• Added 700-MHz C64x+™ device speed.

• Added designators for low-power (-L) devices.

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Section 1.1 Added "5600 MIPS" to "High-Performance Digital Signal Processor (C6421)" bullet

Section 1.2

• In first paragraph, updated/changed the following:

– First sentence from "With performance up to 4800 million instructions per second (MIPS) at a

clock rate of 600 MHz..." to "With performance up to 5600 million instructions per second (MIPS)

with a clock rate of 700 MHz..."

– Fifth sentence from "The DSP core can produce...for a total of 2400 million MACs per second...or

a total of 4800 MMACS." to "The DSP core can produce...for a total of 2800 million MACs per

second...or a total of 5600 MMACS."

Section 2.7 Updated/Changed Figure 2-12 , Device Nomenclature, to reflect new device speeds and low-power

designator (-L suffix).

Section 2.5 Table 2-20 , Multichannel Audio Serial Port (McASP0) Terminal Functions:

• Updated/Changed AFSR0/DR0/GP[100] pin description from "... frame synchronization AFSX0..." to

"...frame synchronization AFSR0..."

• Updated/Changed AFSX0/DX1/GP[107] pin description from "...frame synchronization AFSR0..." to

"...frame synchronization AFSX0..."

Section 2.5 Table 2-25 , Standalone GPIO 3.3 V Terminal Functions:

• Added " Note: GP[xx] is only available when AEM = 0 or 5" to GP[36] through GP[43].

Section 3.7.3.1 Table 3-19 , Multiplexed Pins on C6421:

• Added " Note: GP[43:36] are only available when AEM = 0 or 5" to GP[36] through GP[43].

Section 5.3 Updated/Changed I

CDD

and I

DDD

test conditions and footnote in Section 5.3 , Electrical Characteristics

Over Recommended Ranges of Supply Voltage and Operating Temperature (Unless Otherwise Noted).

Section 5.2 Deleted "Future variants..." footnote from table

Section 6.7.1 Table 6-15 , PLLC1 Clock Frequency Ranges:

• Updated/Changed PLLOUT 1.2V-CV

DD

max value from "700 MHz" to "600 MHz" for

-6/-5/-4/-Q6/-Q5/-Q4 devices.

• Updated/Changed SYSCLK1 1.05V-CV

DD

max value from "560 MHz" to "520 MHz" for -7 devices.

Section 6.7.1 Updated/Changed sentence from "TI requires EMI filter manufacturer Murata..." to "TI recommends EMI

filter manufacturer Murata..."

Section 6.7.4 Deleted "(-4, -4Q, -4S, -5, -5Q, -5S, -6)" from Table 6-19 title, Timing Requirements for MXI/CLKIN.

Revision History6 Submit Documentation Feedback

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件