Datasheet 搜索 > 微处理器 > NXP(恩智浦) > P2020NXN2MHC 数据手册 > P2020NXN2MHC 用户编程技术手册 5/35 页

¥ 1270.897

P2020NXN2MHC 用户编程技术手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

分类:

微处理器

封装:

PBGA-689

描述:

微处理器, QorIQ系列QorIQ P系列, 32位, 1.2 GHz, 0.95V至1.05V, BGA-689

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

P2020NXN2MHC数据手册

Page:

of 35 Go

若手册格式错乱,请下载阅览PDF原文件

PowerQUICC and QorIQ DDR3 SDRAM Controller Register Setting Considerations, Rev. 4

Freescale Semiconductor 5

Register definitions

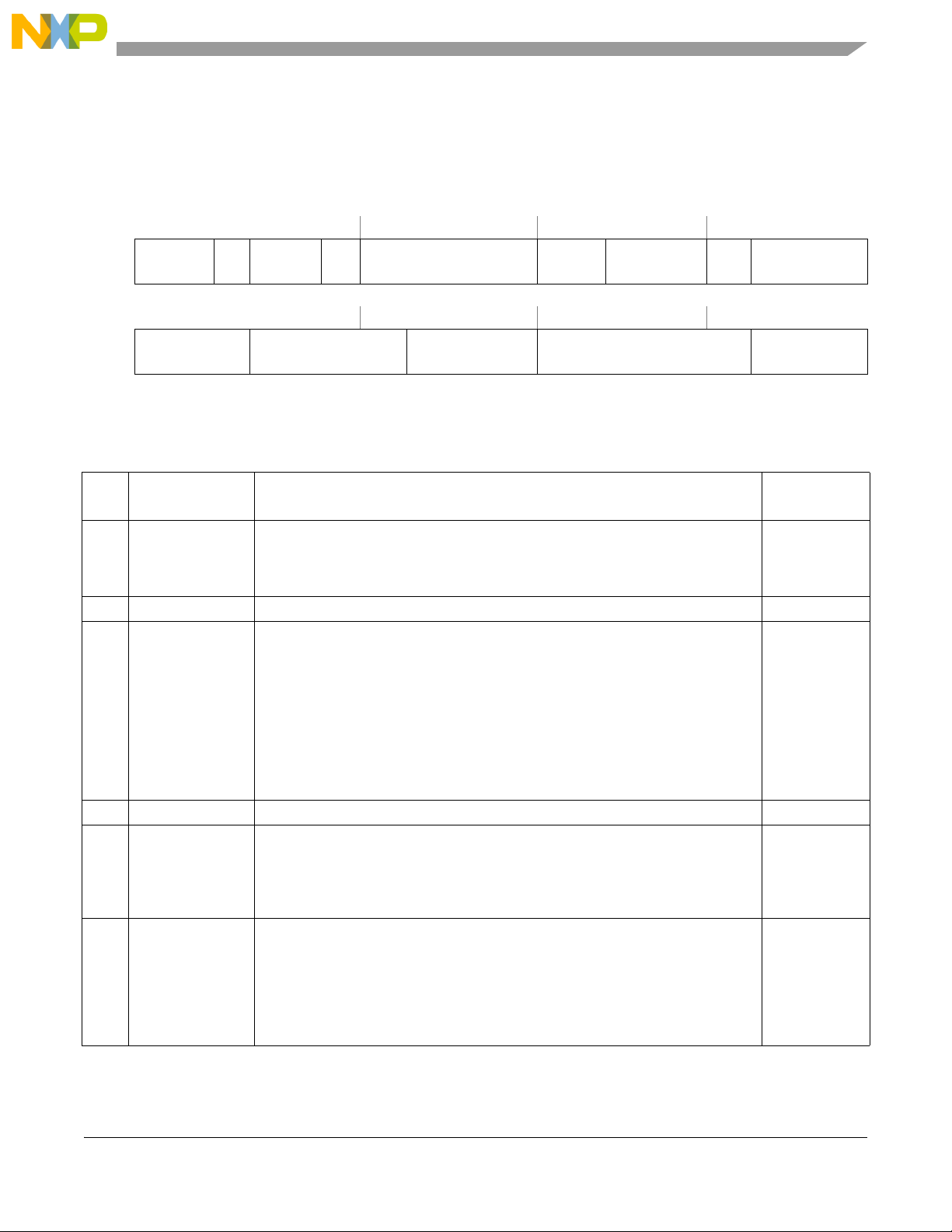

2.2 Chip-Select Configuration Register (CSn_CONFIG)

The chip-select configuration register (CSn_CONFIG), shown in Figure 2, enables DDR chip-select n and

sets the number of row and column bits used for this chip-select.

Table 3 describes the CS_n CONFIG register fields.

Offset 0x080 Access: Read/Write

0 1 2 3 4 7 8 9 11 12 13 15

R

CS_n _EN — INTLV_EN — INTLV_CTL AP_n_EN ODT_RD_CFG — ODT_WR_CFG

W

16 17 18 20 21 23 24 28 29 31

R

BA_BITS_CS_n —ROW_BITS_CS_n — COL_BITS_CS_n

W

Figure 2. Chip-Select Configuration Register (CSn_CONFIG)

Table 3. CS_n CONFIG Register field descriptions

Bits Name Description

Recommended

settings

0CS_n_EN Chip-select n enable

This bit should be set if chip-select n is used in the memory configuration. For

example, set CS0_CONFIG[CS_0_EN] to chip-select 0 in the memory

configuration.

—

1—Reserved 0

2 INTLV_EN Memory controller interleave enable

This field is only available in devices with two or four memory controllers. Set this

bit to enable interleaving between the two or four memory controllers.

This field is only available in CS0_CONFIG register. Size of the memory

interleaved between the two memory controllers must be the same in the

CS0_BOUNDS register. The data bus widths of the two controllers must be the

same. In addition, when enabling this bit, CS0_CONFIG[INTLV_CTL] field must be

set to a valid and same selection in both memory controllers. For further details on

memory controller interleaving, see DDR Interleaving for PowerQUICC and QorIQ

Processors (AN3939).

—

3—Reserved 0

4–7 INTLV_CTL This field is only available in devices with two or four memory controllers. When

interleaving between two memory controller is enabled, choose a valid value from

available selections. Cache line, page, bank, and super-bank interleaving options

are available. For further details on memory controller interleaving, see DDR

Interleaving for PowerQUICC and QorIQ Processors (AN3939).

—

8 AP_n_EN Chip-select n auto-precharge enable

Chip-select n is auto precharged by setting this field (AP_n_EN = 1). In addition,

chip-select n is auto precharged if both this field (AP_n_EN = 0) and the precharge

interval field (DDR_SDRAM_INTERVAL[BSTOPRE] = 0) are cleared.

This field is usually cleared leaving the decision for auto-precharged or not

auto-precharged to the value selected for the precharge interval field (that is,

DDR_SDRAM_INTERVAL[BSTOPRE]).

0

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件