Datasheet 搜索 > 微控制器 > Microchip(微芯) > DSPIC33FJ128GP802-E/MM 数据手册 > DSPIC33FJ128GP802-E/MM 其他数据使用手册 2/30 页

器件3D模型

器件3D模型¥ 50.067

DSPIC33FJ128GP802-E/MM 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

QFN-28

描述:

DSPIC33FJ128GP802-E/MM 管装

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P2P6

导航目录

DSPIC33FJ128GP802-E/MM数据手册

Page:

of 30 Go

若手册格式错乱,请下载阅览PDF原文件

AN1249

DS01249A-page 2 © 2009 Microchip Technology Inc.

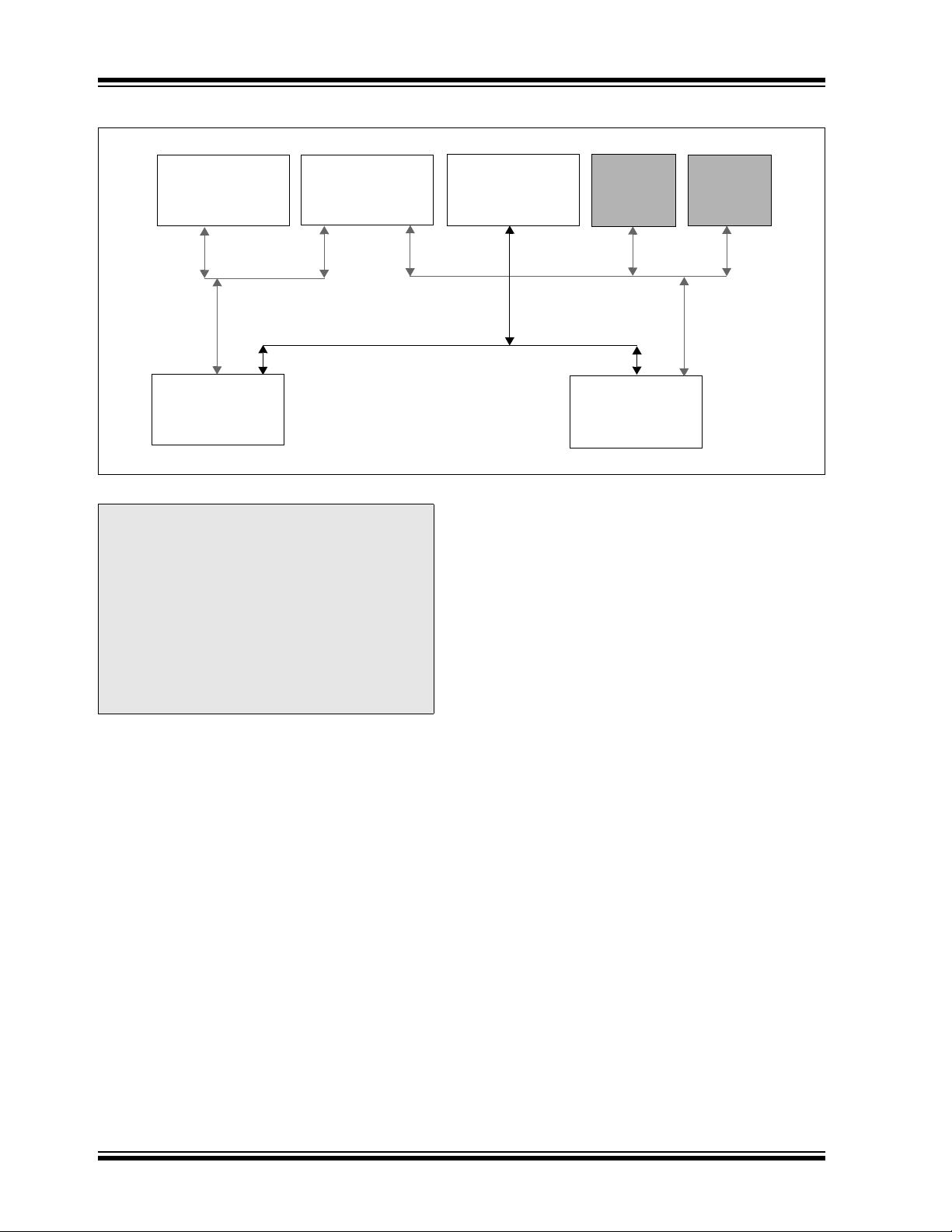

FIGURE 1: ECAN™ DMA BLOCK DIAGRAM

Microchip’s ECAN module on the dsPIC33F or PIC24H

device can be used with or without DMA to send and

receive messages. The biggest advantage of using

DMA with ECAN is that the data can be moved without

involving the CPU or stealing CPU cycles. This

implementation is optimized for performance of a

real-time embedded application where system latency

is a priority and CPU timing must be predictable.

CAN Data Frames

A CAN network can be configured to communicate with

both of the following formats:

• Standard format - intended for standard

messages that use 11 identifier bits

• Extended format - intended for extended

messages that use 29 identifier bits

The ECAN module on the dsPIC33F and PIC24H

devices supports both the standard and extended

formats.

The ECAN module distinguishes between the CAN

standard frame and CAN extended frame using the IDE

bit, which is part of the ECAN message that is

transmitted as dominant (logical ‘0’) for an 11-bit frame

(standard), and recessive (logical ‘1’) for a 29-bit frame

(extended).

The CAN bus frame consists of two main fields:

• User-controlled field

• Module-controlled field

The user specifies the ID and message data to which

the ECAN module adds the applicable fields to ensure

that the message frame meets the CAN specification.

SRAM

DPSRAM

DMA Controller

CPU

ECAN™

CPU

DMA

PORT1

PORT2

CPU X-bus

DMA X-bus

CPU Peripheral X-bus

Channel X

Channel Y

Note: Microchip’s 16-bit CPU architecture is

capable of read and write access within

each CPU bus cycle. The DMA read and

write timing is the same as the CPU

timing, and can complete the transfer of a

byte or a word in every bus cycle across its

dedicated bus. This also guarantees that

all DMA transfers are atomic. This ensures

that once the data transfer has started, it is

completed within the same cycle,

regardless of the activity of other

channels.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件