Datasheet 搜索 > TI(德州仪器) > CDCLVD110 数据手册 > CDCLVD110 用户编程技术手册 4/14 页

¥ 0

CDCLVD110 用户编程技术手册 - TI(德州仪器)

制造商:

TI(德州仪器)

描述:

具有最低时钟失真斜率最高 900MHz 的 1 至 10 LVDS 时钟缓冲器

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

CDCLVD110数据手册

Page:

of 14 Go

若手册格式错乱,请下载阅览PDF原文件

www.ti.com

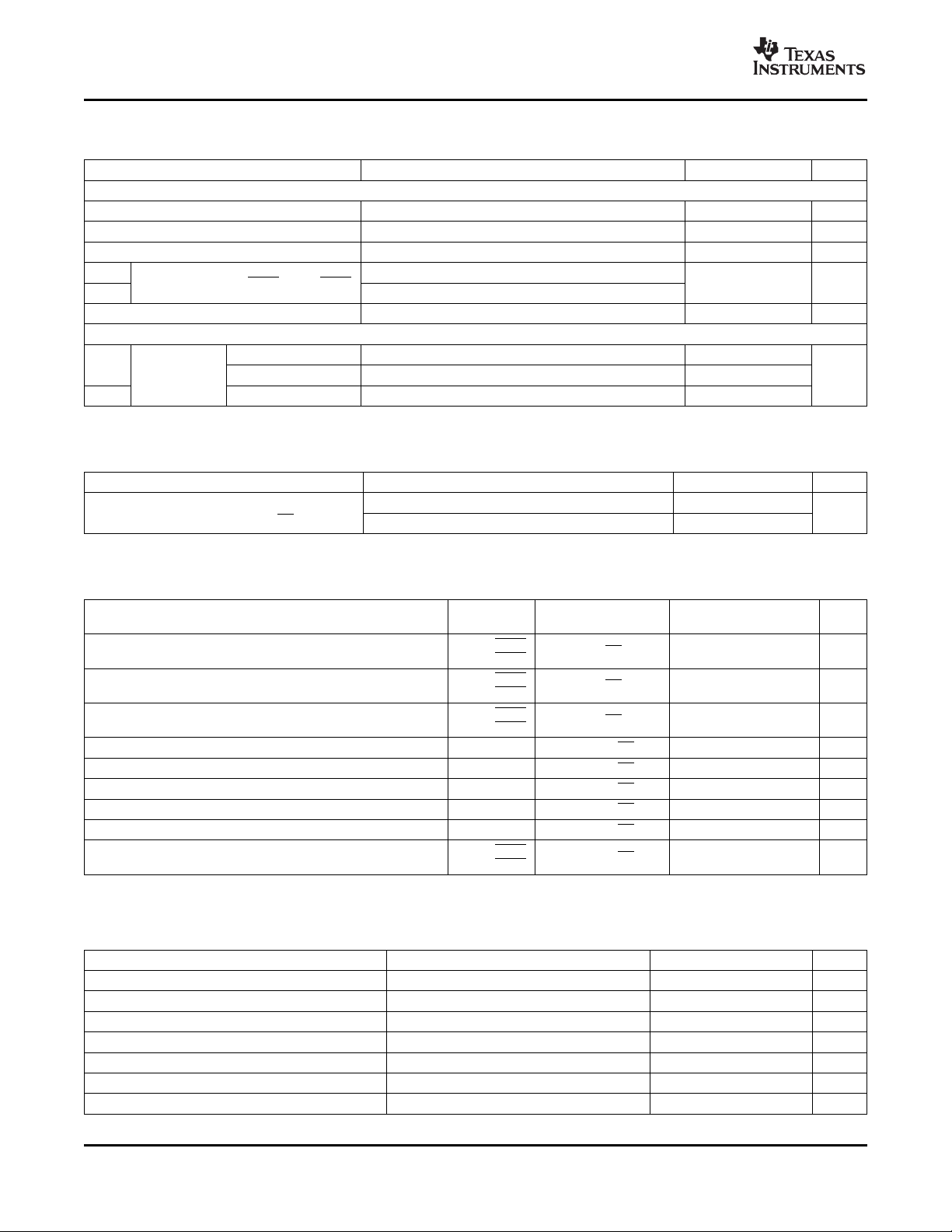

JITTER CHARACTERISTICS

LVDS — SWITCHING CHARACTERISTICS

CONTROL REGISTER CHARACTERISTICS

CDCLVD110

SCAS684C – SEPTEMBER 2002 – REVISED JANUARY 2008

ELECTRICAL CHARACTERISTICS (continued)

over recommended operating free-air temperature range (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

RECEIVER

V

IDH

Input threshold high 100 mV

V

IDL

Input threshold low – 100 mV

|V

ID

| Input differential voltage 200 mV

I

IH

V

I

= V

DD

Input current, CLK0/ CLK0, CLK1/ CLK1 – 5 5 µ A

I

IL

V

I

= 0 V

C

I

Input capacitance V

I

= V

DD

or GND 3 pF

SUPPLY CURRENT

Full loaded All outputs enabled and loaded, R

L

= 100 Ω , f = 0 Hz 130

I

DD

Supply current No load Outputs enabled, no output load, f = 0 Hz 35 mA

I

DDZ

3-State All outputs 3-state by control logic, f = 0 Hz 35

characterized with CDCLVD110 performance EVM, V

DD

= 3.3 V, OUTPUTS NOT UNDER TEST are terminated to 50 Ω

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

12 kHz to 5 MHz, f

out

= 30.72 MHz 650

Additive phase jitter from input to

t

jitterLVDS

fs rms

LVDS output Q3 and Q3

12 kHz to 20 MHz, f

out

= 125 MHz 299

over recommended operating free-air temperature range, V

DD

= 2.5 V ± 5%

FROM TO

PARAMETER MIN TYP MAX UNIT

(INPUT) (OUTPUT)

CLK0, CLK0

t

PLH

Propagation delay low-to-high Qn, Qn 2 3 ns

CLK1, CLK1

Propagation delay high-to-low CLK0, CLK0

t

PHL

Qn, Qn 2 3 ns

CLK1, CLK1

CLK0, CLK0

t

duty

Duty cycle Qn, Qn 45% 55%

CLK1, CLK1

t

sk(o)

Output skew Any Qn, Qn 30 ps

t

sk(p)

Pulse skew Any Qn, Qn 50 ps

t

sk(pp)

Part-to-part skew Any Qn, Qn 600 ps

t

r

Output rise time, 20% to 80%, R

L

= 100 Ω , C

L

= 5 pF Any Qn, Qn 350 ps

t

f

Output fall time, 20% to 80%, R

L

= 100 Ω , C

L

= 5 pF Any Qn, Qn 350 ps

CLK0, CLK0

f

clk

Max input frequency Any Qn, Qn 900 1100 MHz

CLK1, CLK1

over recommended operating free-air temperature range, V

DD

= 2.5 V ± 5% (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

f

MAX

Maximum frequency of shift register 100 150 MHz

t

su

Setup time, clock to SI 2 ns

t

h

Hold time, clock to SI 1.5 ns

t

removal

Removal time, enable to clock 1.5 ns

t

w

Clock pulse width, minimum 3 ns

V

IH

Logic input high V

DD

= 2.5 V 2 V

V

IL

Logic input low V

DD

= 2.5 V 0.8 V

4 Submit Documentation Feedback Copyright © 2002 – 2008, Texas Instruments Incorporated

Product Folder Link(s) :CDCLVD110

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件