Datasheet 搜索 > 微控制器 > NXP(恩智浦) > MC56F8006VLC 数据手册 > MC56F8006VLC 用户编程技术手册 1/106 页

器件3D模型

器件3D模型¥ 26.801

MC56F8006VLC 用户编程技术手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

分类:

微控制器

封装:

LQFP-32

描述:

NXP MC56F8006VLC 芯片, 数字信号控制器, 16位, 32MHZ, 16KB, 32LQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P13Hot

原理图在P4P9

封装尺寸在P18P19P20P21P22P23P24P25P26P27P28P73

型号编码规则在P72

技术参数、封装参数在P1P11P41P42P43P44P45P46P47P48P49P50

电气规格在P46P57

导航目录

MC56F8006VLC数据手册

Page:

of 106 Go

若手册格式错乱,请下载阅览PDF原文件

Freescale Semiconductor

Technical Data

Document Number: MC56F8006

Rev. 4, 06/2011

© Freescale Semiconductor, Inc., 2009–2011. All rights reserved.

Freescale reserves the right to change the detail specifications as may be required to permit

improvements in the design of its products.

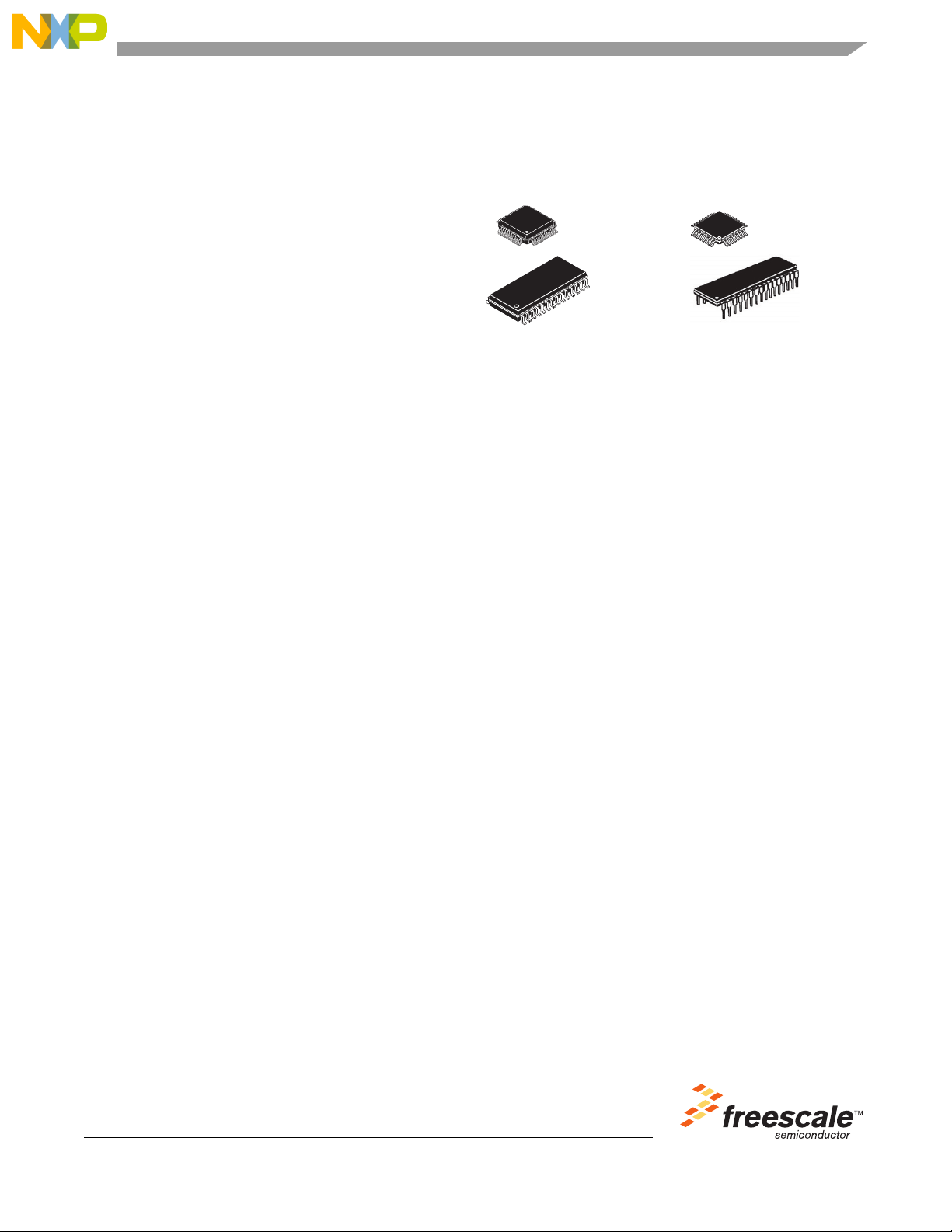

MC56F8006/MC56F8002

48-pin LQFP

Case: 932-03

7 x 7 mm

2

28-pin SOIC

Case: 751F-05

7.5 x 18 mm

2

32-pin LQFP

Case: 873A-03

7 x 7 mm

2

32-pin PSDIP

Case: 1376-02

9 x 28.5 mm

2

This document applies to parts marked with 2M53M.

The 56F8006/56F8002 is a member of the 56800E core-based

family of digital signal controllers (DSCs). It combines, on a

single chip, the processing power of a DSP and the

functionality of a microcontroller with a flexible set of

peripherals to create a cost-effective solution. Because of its

low cost, configuration flexibility, and compact program

code, the 56F8006/56F8002 is well-suited for many

applications. It includes many peripherals that are especially

useful for cost-sensitive applications, including:

• Industrial control

• Home appliances

• Smart sensors

• Fire and security systems

• Switched-mode power supply and power management

•Power metering

• Motor control (ACIM, BLDC, PMSM, SR, and stepper)

• Handheld power tools

• Arc detection

• Medical device/equipment

• Instrumentation

• Lighting ballast

The 56800E core is based on a dual Harvard-style architecture

consisting of three execution units operating in parallel, allowing

as many as six operations per instruction cycle. The MCU-style

programming model and optimized instruction set allow

straightforward generation of efficient, compact DSP and control

code. The instruction set is also highly efficient for C compilers

to enable rapid development of optimized control applications.

The 56F8006/56F8002 supports program execution from internal

memories. Two data operands can be accessed from the on-chip

data RAM per instruction cycle. The 56F8006/56F8002 also

offers up to 40 general-purpose input/output (GPIO) lines,

depending on peripheral configuration.

The 56F8006/56F8002 digital signal controller includes up to

16 KB of program flash and 2 KB of unified data/program

RAM. Program flash memory can be independently bulk

erased or erased in small pages of 512 bytes (256 words).

On-chip features include:

• Up to 32 MIPS at 32 MHz core frequency

• DSP and MCU functionality in a unified, C-efficient

architecture

• On-chip memory

– 56F8006: 16 KB (8K x 16) flash memory

– 56F8002: 12 KB (6K x 16) flash memory

– 2 KB (1K x 16) unified data/program RAM

• One 6-channel PWM module

• Two 28-channel, 12-bit analog-to-digital converters

(ADCs)

• Two programmable gain amplifiers (PGA) with gain up to

32x

• Three analog comparators

• One programmable interval timer (PIT)

• One high-speed serial communication interface (SCI) with

LIN slave functionality

• One serial peripheral interface (SPI)

• One 16-bit dual timer (2 x 16 bit timers)

• One programmable delay block (PDB)

• One SMBus compatible inter-integrated circuit (I

2

C) port

• One real time counter (RTC)

• Computer operating properly (COP)/watchdog

• Two on-chip relaxation oscillators — 1 kHz and 8 MHz

(400 kHz at standby mode)

• Crystal oscillator

• Integrated power-on reset (POR) and low-voltage interrupt

(LVI) module

• JTAG/enhanced on-chip emulation (OnCE™) for

unobtrusive, real-time debugging

• Up to 40 GPIO lines

• 28-pin SOIC, 32-pin LQFP, 32-pin PSDIP, and 48-pin

LQFP packages

MC56F8006/MC56F8002

Digital Signal Controller

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件